# UNIDEX 16 MAINTENENCE CLASS

# PART 1

# MICRO SECTION

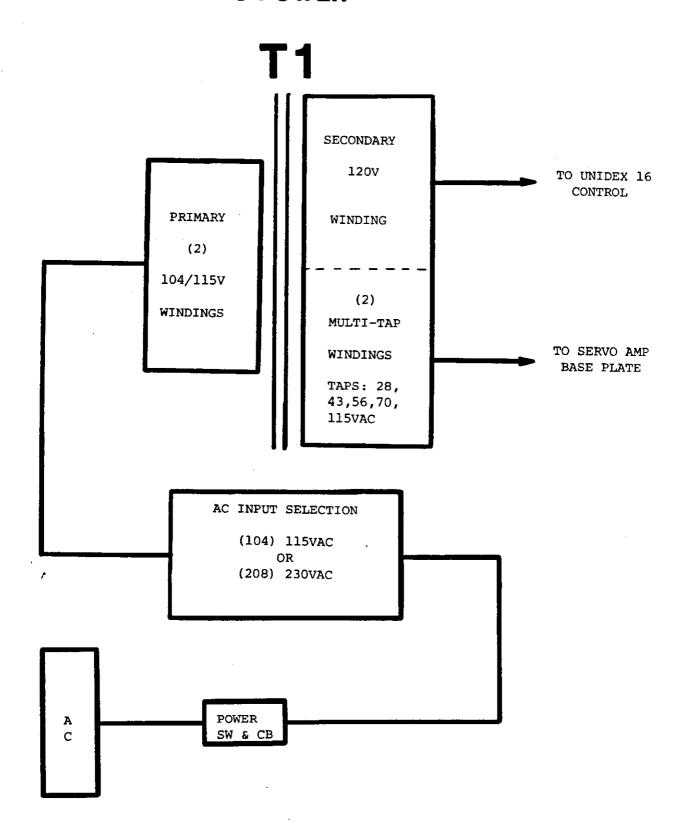

# **AC POWER**

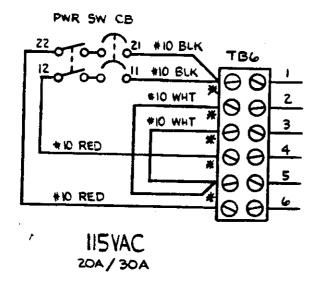

SINGLE PHASE

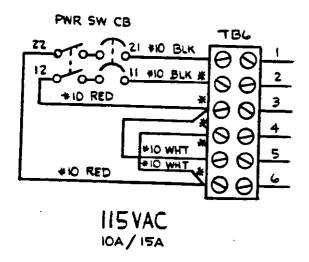

# AC INPUT SELECTION

\* TB6 USES RING TONGUE LUGS EXCEPT WHERE NOTED (\*) WHICH USES SPADE LUGS

ITB 2-2

IM

\* OPTIONAL DR NOT AVAILABLE ON ALL MODELS

IM IT82-

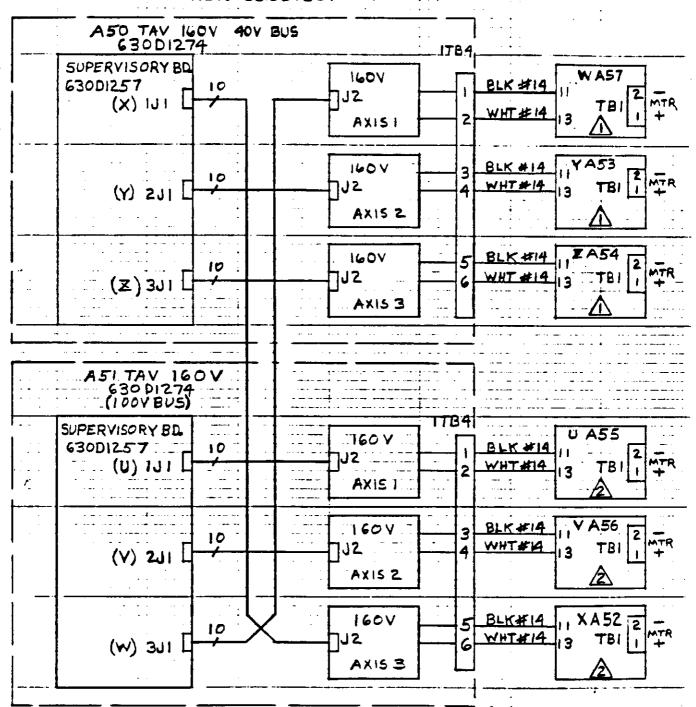

1/2·A50 SERVO CONTROL

BASE PLATE

T1

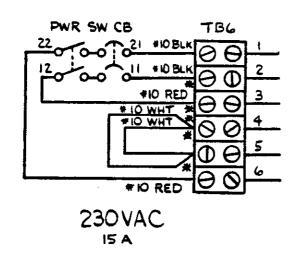

# TV2.5/TV5A

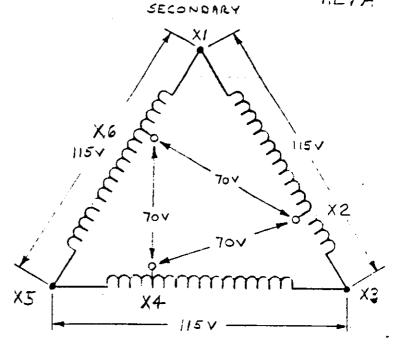

RE1A

DUAL FRIMARY 230/460 WITH TAPS FOR:

208 U C O O A Q U C C S53 C T C C T C S53 C T C C T C S53 C T C T C C T C C T C C T C T C C T C T C C T C T C C T C T C C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C T C

H3 A B U D O A 2 U D D 253

115 V 30 DELTA @ 6KVA TOV 30 DELTA @ 6KVA

ZKVA PEAK

41 TERMINALS TOTAL

5% REGULATION

180°C

0

**T83**

12

TB5

0

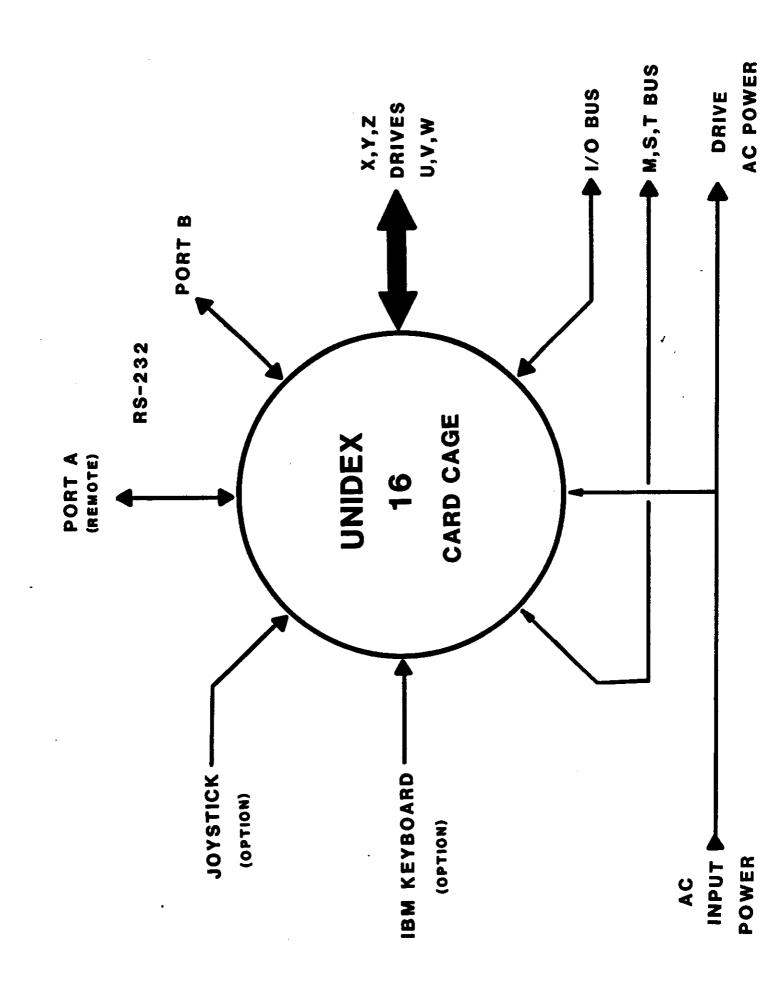

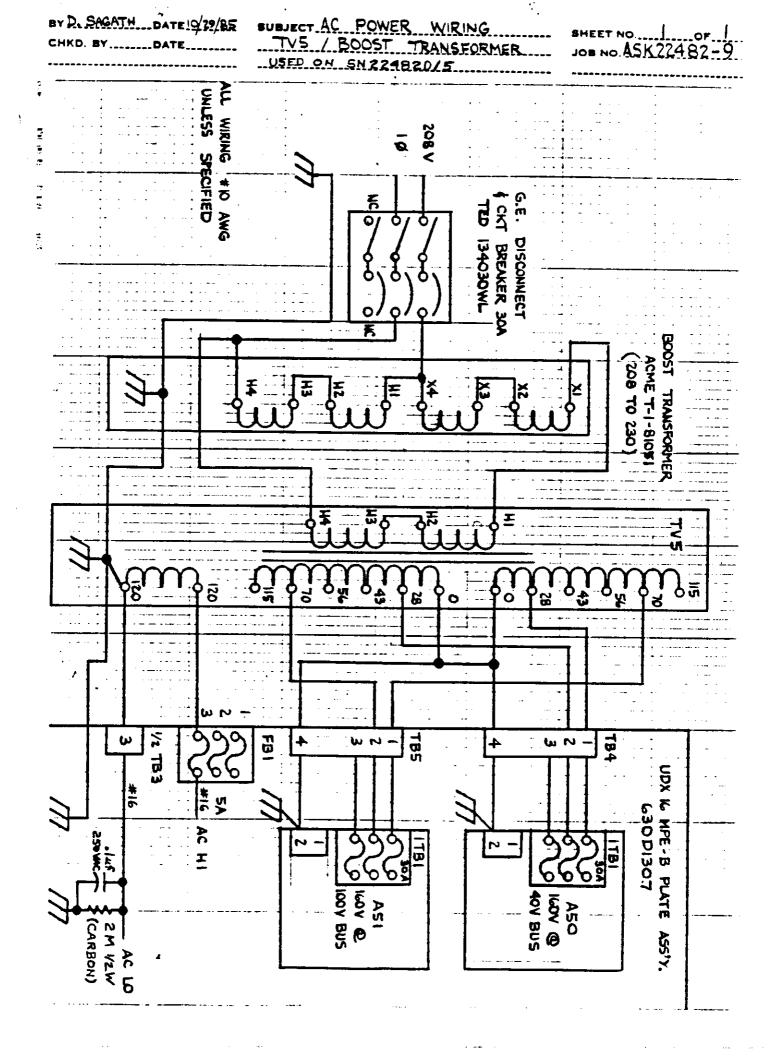

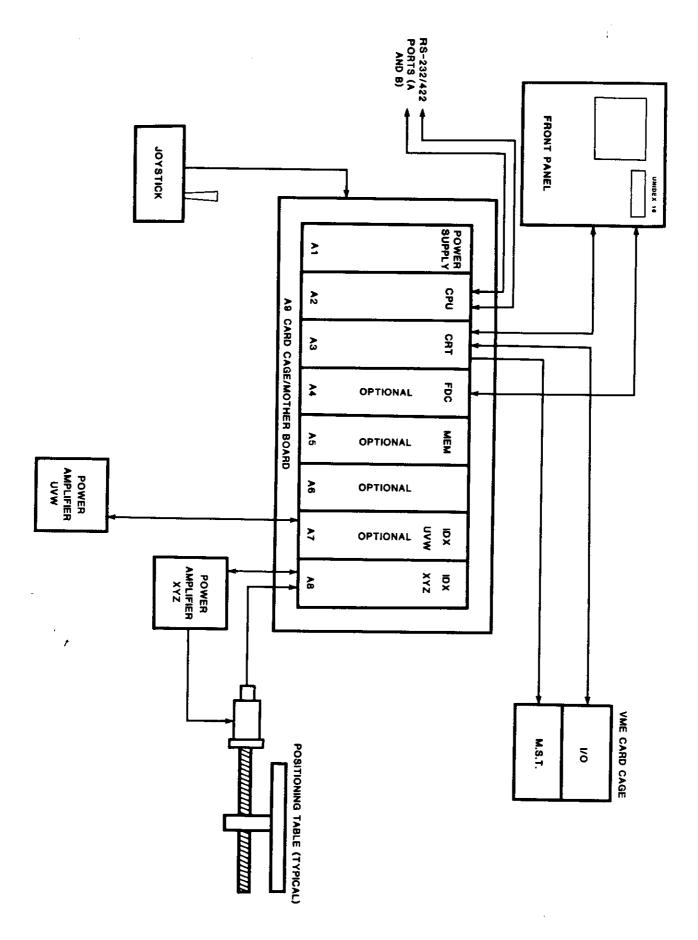

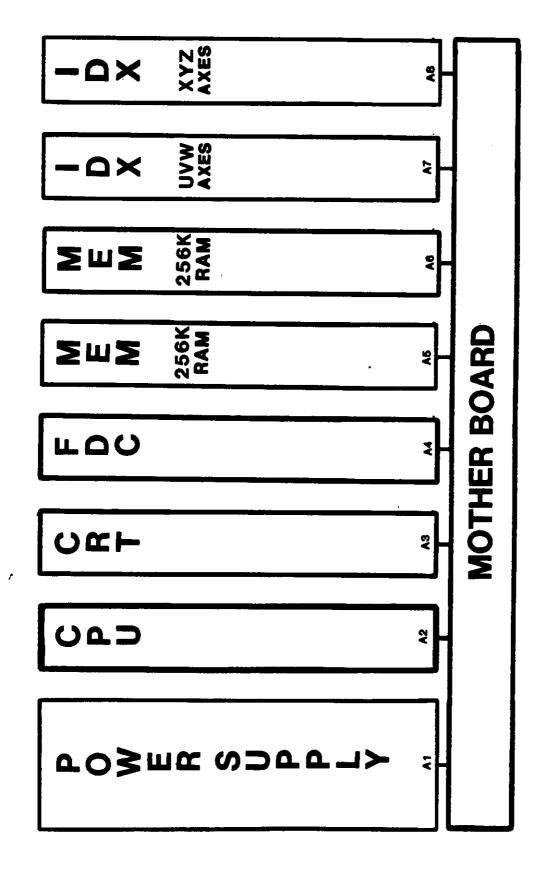

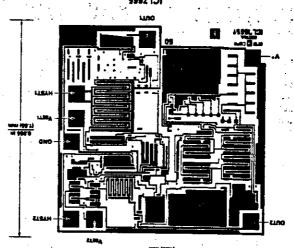

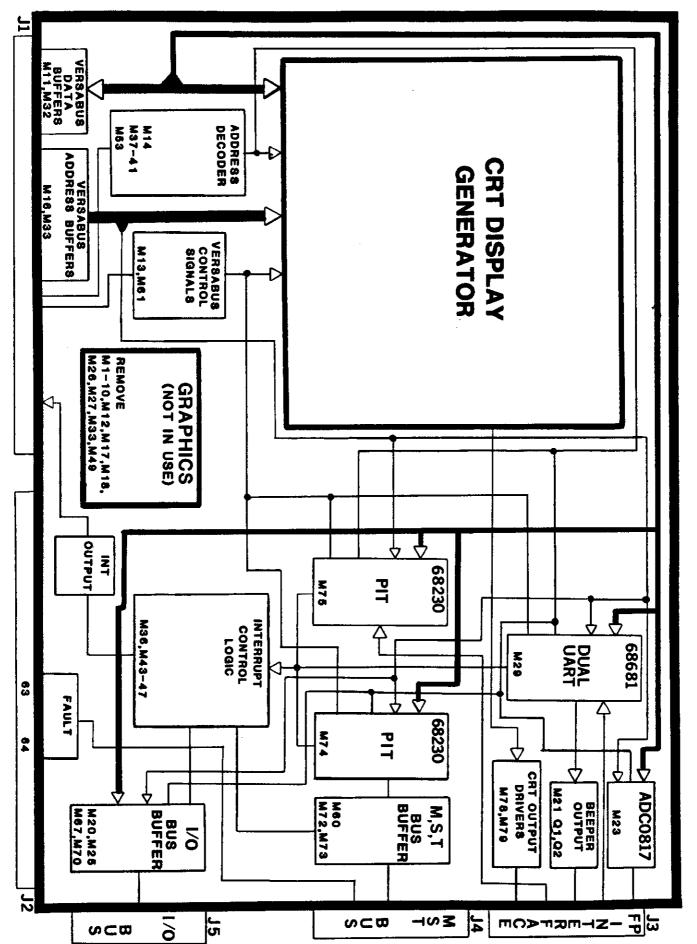

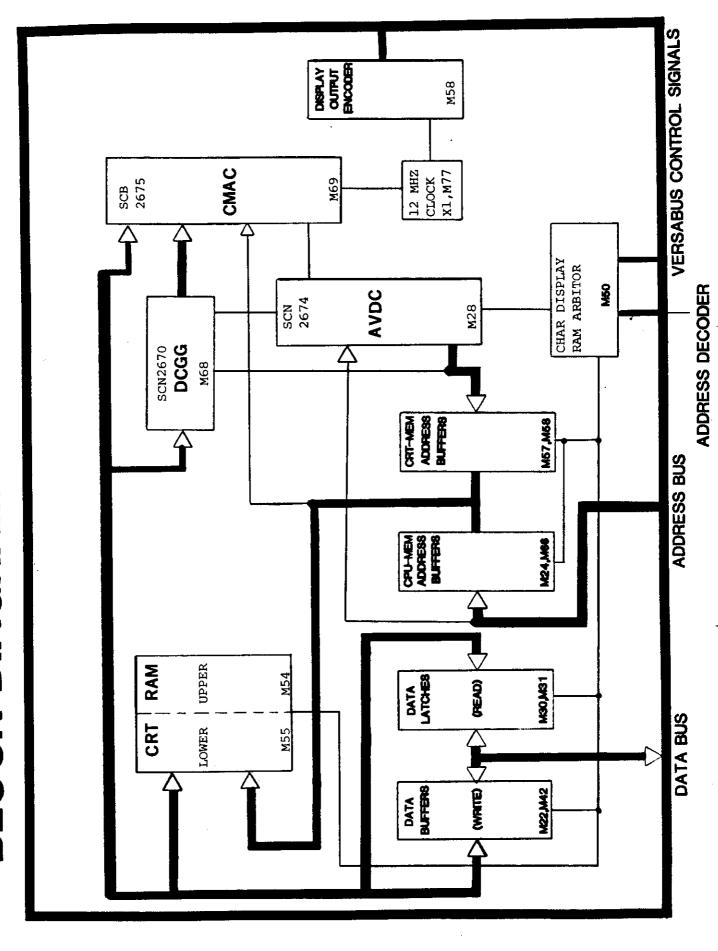

# UNIDEX 16 CARD CAGE

# CARD CAGE

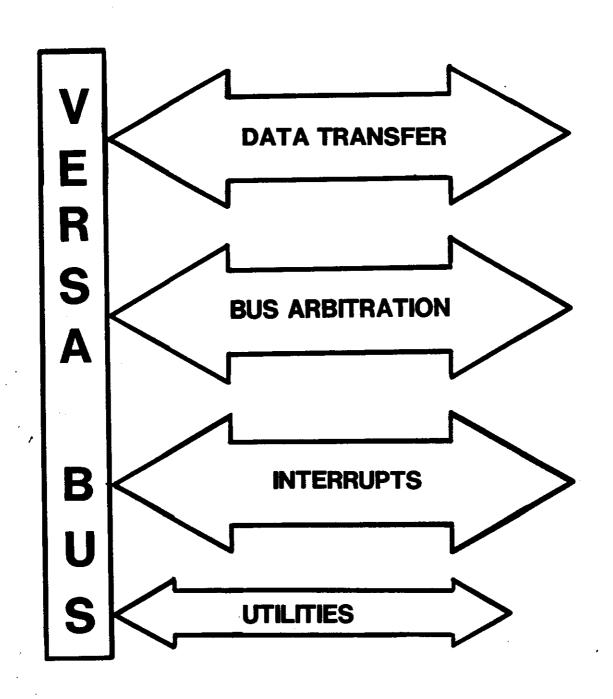

# **VERSABUS**

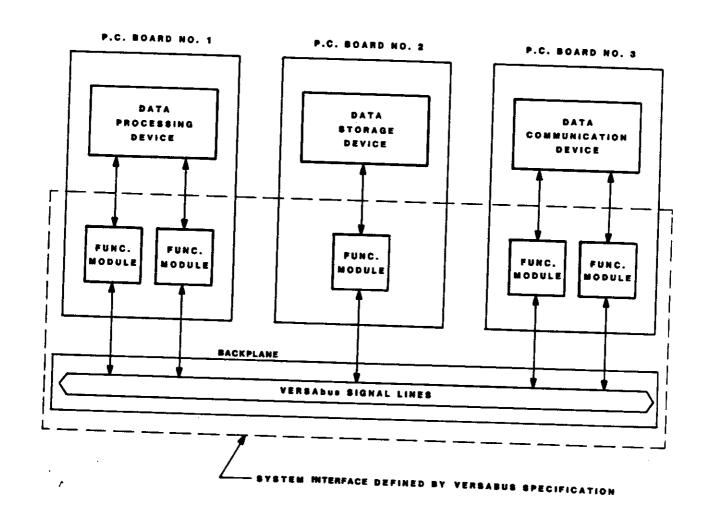

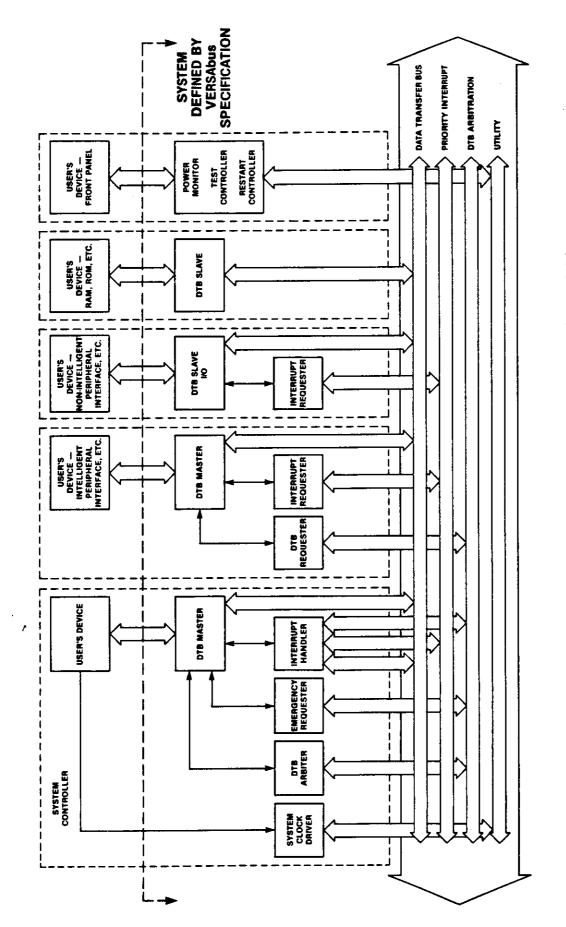

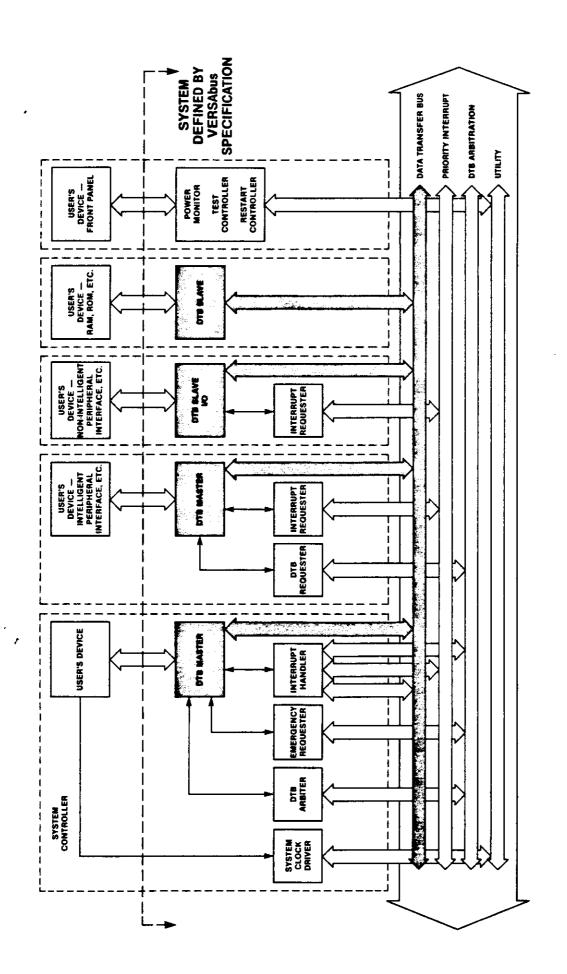

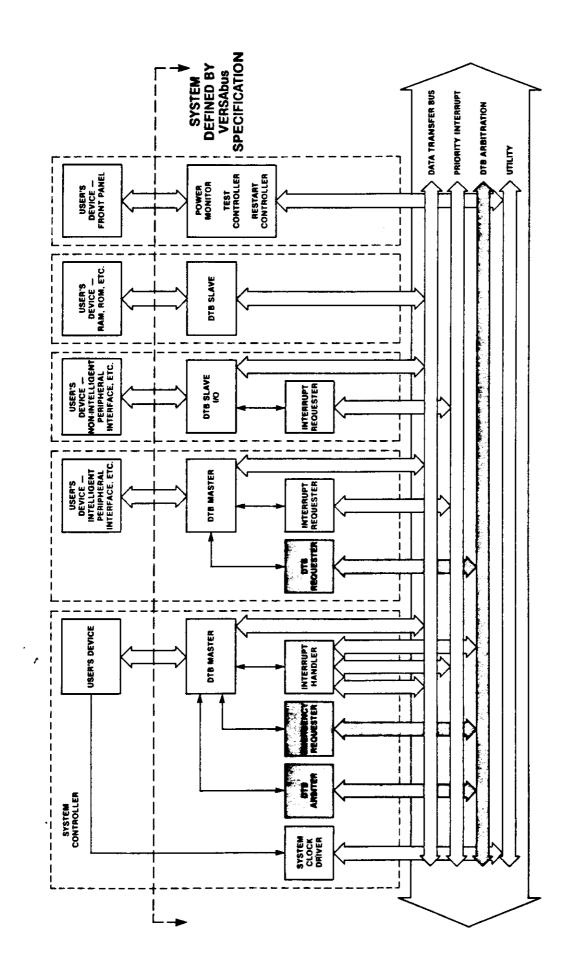

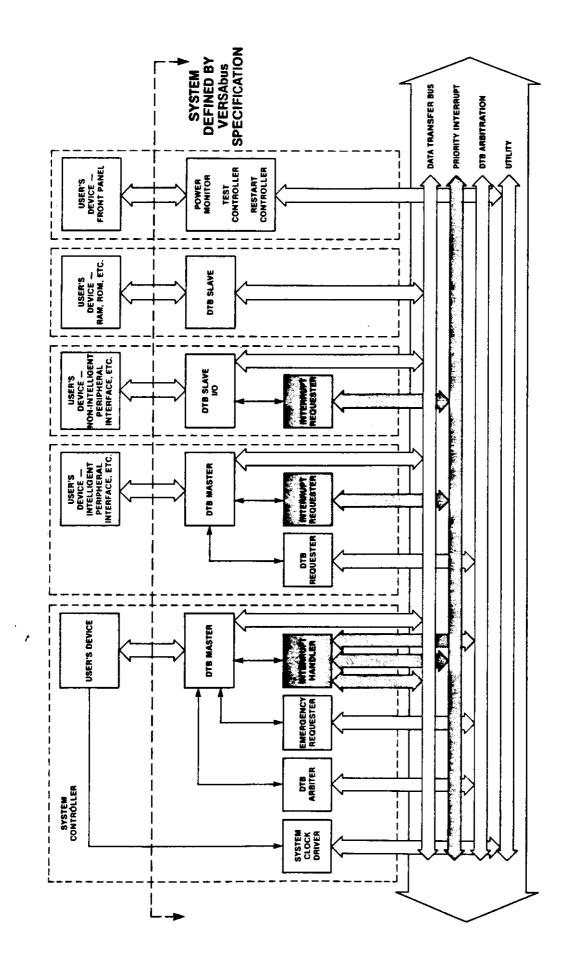

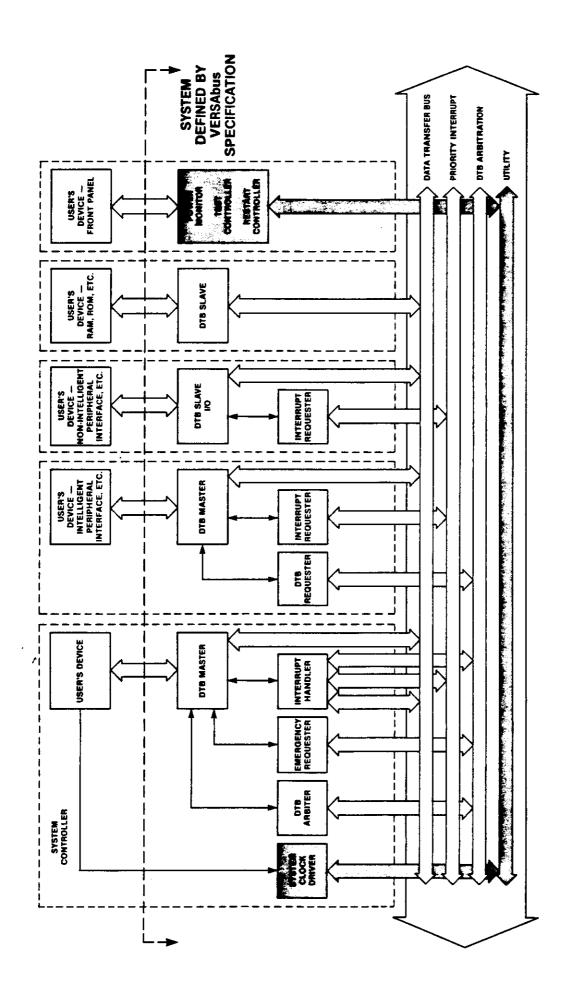

FIGURE 1-2. System Elements Defined by the VERSAbus Specification

FIGURE 1-3. Functional Modules and Buses contained within the VERSAbus Definition

TABLE 1-1. VERSAbus Signal Line Terminology

| _   |                                                                                   |                                                                                                                                                                                                                                                                                                  |                                                                                                                                | ASO JUNI MOSH                                                                                                                            |                                                                                               |

|-----|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

|     | SIGNAL LINE                                                                       |                                                                                                                                                                                                                                                                                                  | SA FOLIA                                                                                                                       | HANT                                                                                                                                     | ASTRED TSK                                                                                    |

|     | CATESORY                                                                          | MINEMONICS (1)                                                                                                                                                                                                                                                                                   | College                                                                                                                        | TOANT                                                                                                                                    | VICTORIO                                                                                      |

|     | BUS LINES<br>(Three-state)                                                        | A01*-A31* D00*-D31* APARITYO*-APARITY1* DPARITYO*-DPARITY3* AMO*-AM7* TESTO*-TEST1* WRITE*, LWORD*                                                                                                                                                                                               | Drive X Drive X high Drive X low Place valid X Remove X Release X                                                              | Receive X driven high<br>Receive X driven low<br>Receive X                                                                               | Indicates a low level<br>Equals a logic l                                                     |

|     | Drive X defines Place valid X demove X defines Remove X defines Release X defines | Drive X defines the point at which the three-state drivers are enabled. Place valid X defines the point at which the levels on the bus are valid. Remove X defines the point at which the levels on the bus are invalid. Release X defines the point at which the three-state drivers are no lon | ree-state drivers are enabled. the levels on the bus are valid. evels on the bus are invalid. three-state drivers are no longe | ree-state drivers are enabled. the levels on the bus are valid. evels on the bus are invalid. three-state drivers are no longer enabled. |                                                                                               |

| 1-9 | STROBE LINES<br>(Three-state)                                                     | AS*<br>DSO*<br>DS1*                                                                                                                                                                                                                                                                              | Drive X to low<br>Drive X to high                                                                                              | Receive X driven to low<br>Receive X driven to high                                                                                      | Indicates the information on the strobed bus is valid on the falling edge of the strobe line. |

| · . | STROBE RESPONSE<br>LINES<br>(Open Collector)                                      | DTACK*<br>BERR*                                                                                                                                                                                                                                                                                  | Drive X to low<br>Release X to high                                                                                            | Receive X driven to low<br>Receive X high                                                                                                | Indicates the strobe response is valid on the falling edge of the signal line.                |

|     | SHARED LINES<br>(Open Collector)                                                  | IRQ1*-IRQ7*<br>BR0*-BR4*<br>SYSFALL*                                                                                                                                                                                                                                                             | Hold X low<br>Release X                                                                                                        | Detect X low Detect X high (only if no drivers holding line low)                                                                         | Indicates this line is<br>activated in the low<br>state.                                      |

|     | (1) For otl                                                                       | For other signal lines, see subpa                                                                                                                                                                                                                                                                | paragraphs 1.4.3 and 1.4.8.                                                                                                    | 1.4.8.                                                                                                                                   |                                                                                               |

| _   |                                                                                   |                                                                                                                                                                                                                                                                                                  |                                                                                                                                |                                                                                                                                          |                                                                                               |

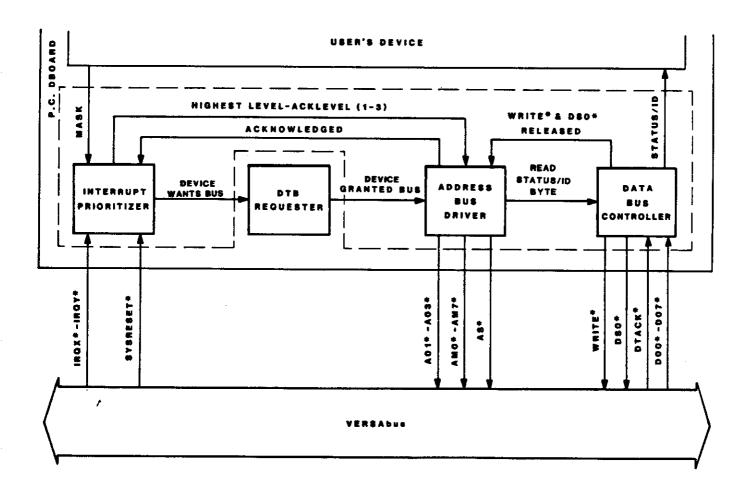

FIGURE 2-1. VERSAbus Data Transfer Functional Block Diagram

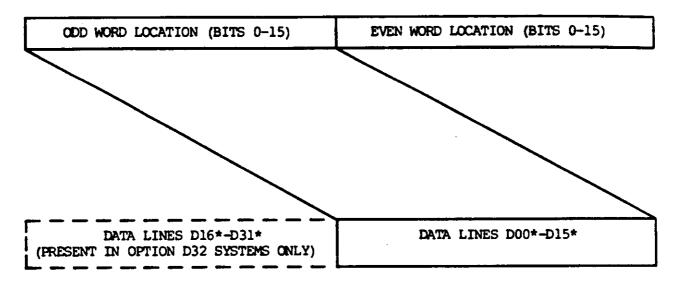

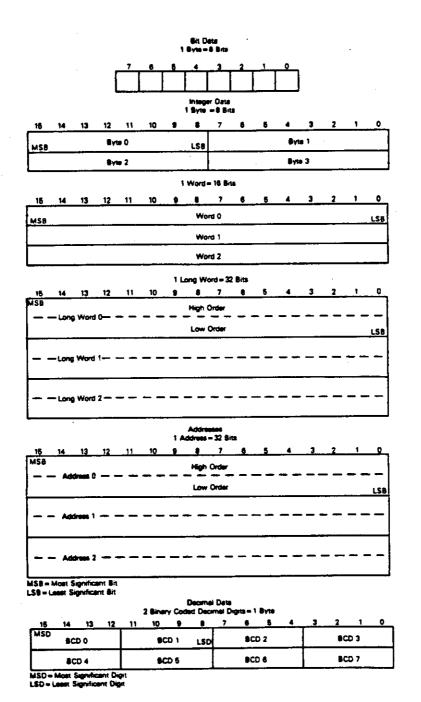

### LONGWORD LOCATION (BITS 0-31)

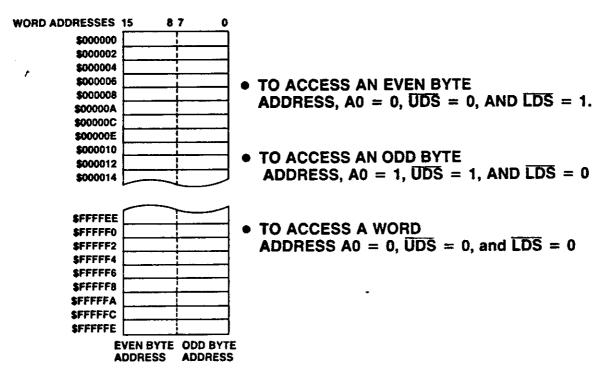

FOR A WORD ACCESS, THE DATA IS ALWAYS TRANSFERRED ON DOO\*-D15\*.

FIGURE 2-4. Odd Word Location Accesses

THE ODD WORD LOCATION (A01 = 1) CORRESPONDS TO THE LONGWORD DATA BITS  $D00^* - D15^*$ .

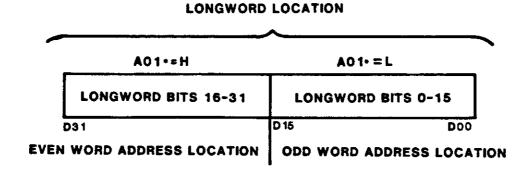

FIGURE 2-5. Word Addressing of LONGWORD Locations

## **LONGWORD LOCATION**

| EVE                                   | EN WORD ADDRES              | S LOCATION               | ODD WORD ADDRESS LOCATION |                            |                            |  |

|---------------------------------------|-----------------------------|--------------------------|---------------------------|----------------------------|----------------------------|--|

| LONGWORD                              | EVEN BYTE LOCATION          | ODD BYTE<br>LOCATION     | EVEN BYTE<br>LOCATION     | ODD B                      |                            |  |

|                                       | D31                         | D23                      | D15                       | D07                        | D00                        |  |

| Byte Address                          | <b>xxx</b> 00               | xx                       | <b>X</b> 01               | <b>XXX</b> X10             | <b>x</b> xx                |  |

| Byte Access LWORD* A01* DS1* DS0*     | high<br>high<br>low<br>high | hig<br>hig<br>hig<br>low | h<br>h                    | high<br>low<br>low<br>high | high<br>low<br>high<br>low |  |

| Word Access LWORD* A01* DS1* DS0*     | high<br>high<br>low<br>low  | Note<br>1                |                           | high<br>low<br>low<br>low  |                            |  |

| LONGWORD Access LWORD* A01* DS1* DS0* | low<br>high<br>low<br>low   | Not<br>2                 |                           | Note<br>3                  | Note<br>2 &                |  |

# NOTES:

- 1. Not legal to access 16 bits of data on an odd byte address.

- 2. Not legal to access 32 bits of data on an odd byte address.

- 3. Not legal to access 32 bits of data on an odd word address.

FIGURE 2-6. Byte Location Numbering

FIGURE 3-1. VERSAbus Arbitration Functional Block Diagram

FIGURE 4-3. VERSAbus Priority Interrupt Functional Block Diagram

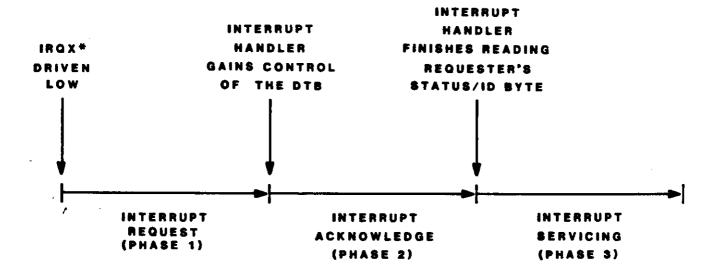

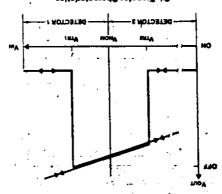

FIGURE 4-6. The Three Phases of an Interrupt Sequence

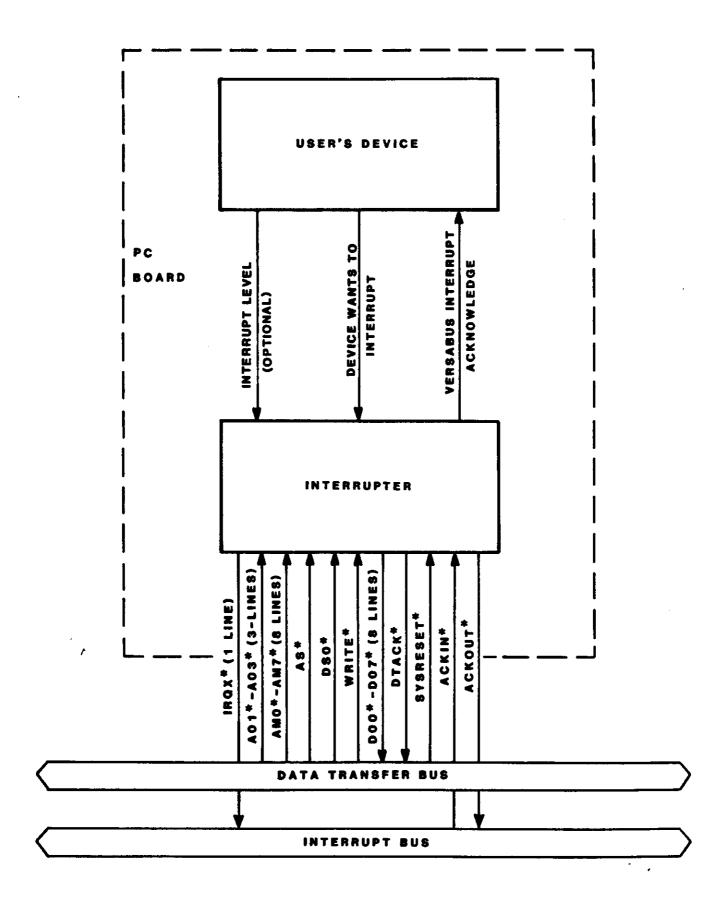

FIGURE 4-13. INTERRUPTER Block Diagram

### 4.5.2 INTERRUPT HANDLER

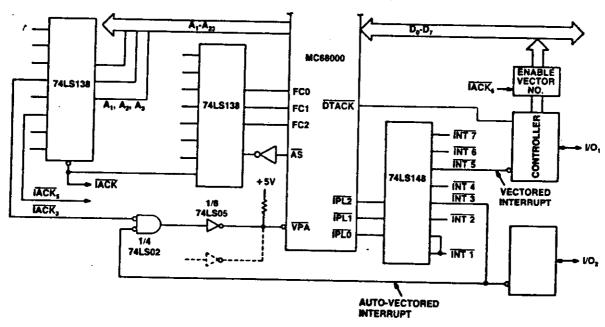

Figure 4-14 shows the block diagram of an INTERRUPT HANDLER. The INTERRUPT HANDLER consists of three sub-elements:

- a. Interrupt prioritizer

- b. Address bus driver

- c. Data bus controller

FIGURE 4-14. Block Diagram: INTERRUPT HANDLER

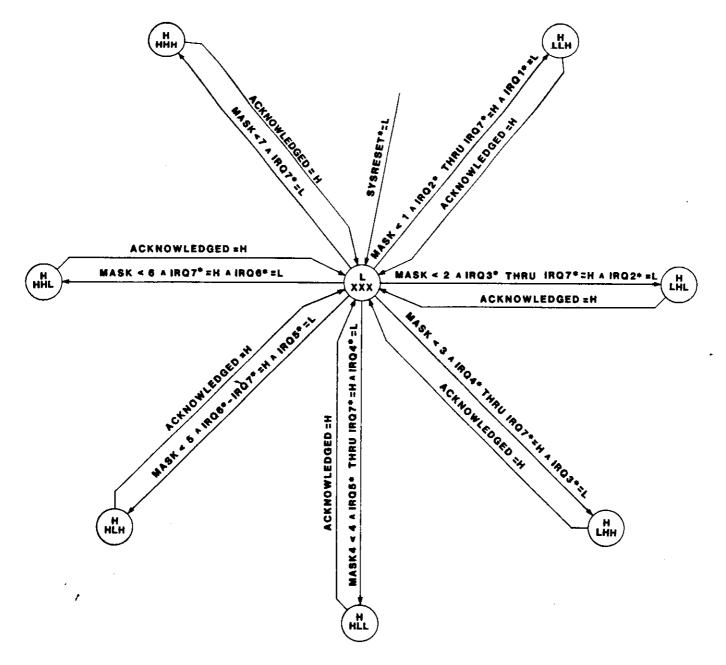

THE STATES ON THIS DIAGRAM ARE LABELLED ACCORDING TO THE LEVELS OF THE INTERRUPT PRIORITIZERS OUTPUT LINES.

| DE      | VICE WANTS B | US      |

|---------|--------------|---------|

| ACK     | ACK          | ACK     |

| LEVEL 3 | LEVEL 2      | LEVEL 1 |

FIGURE 4-15. State Diagram for the Interrupt Prioritizer of a Seven Level INTERRUPT HANDLER

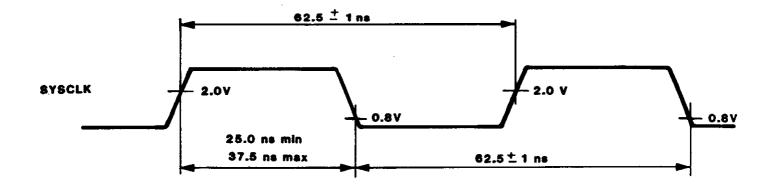

FIGURE 5-1. VERSAbus Utility Block Diagram

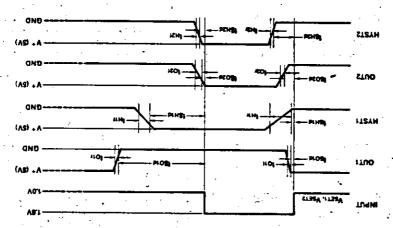

FIGURE 5-2. System Clock Timing Diagram

# 5.2.1.2 AC Clock (ACCLK) Specification

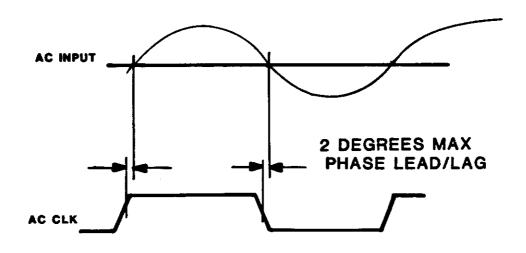

The AC clock is a 50 or 60 hertz (nominal) signal derived from the power supply line frequency. It can be used as a clock source to generate time-of-day, or to detect line frequency zero-point crossings. Figure 5-3 illustrates the timing relationship between the edges of ACCLK and the zero crossings of the AC line. ACCLK edges may lead or lag the AC zero crossing by a maximum of 115 usecs on a 50 cycle system, or 95 usecs on a 60 cycle system.

FIGURE 5-3. AC Clock Timing Diagram

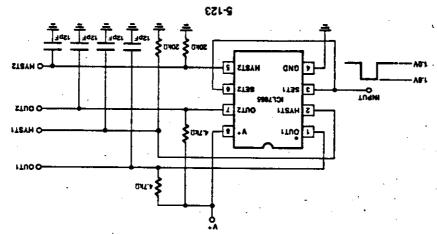

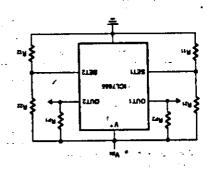

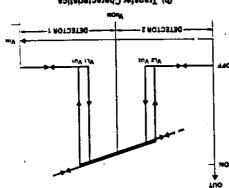

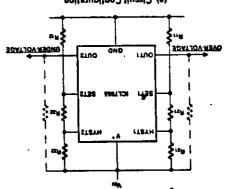

### 5.3 POWER MONITOR MODULE

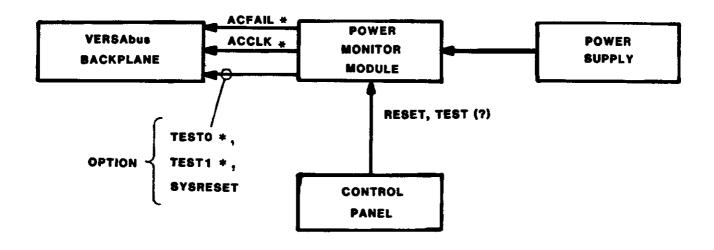

This module is usually an external PC board (Figure 5-5) upon which the ACFAIL\*, ACCLK, and (optionally) TESTO\*, TESTI\*, and SYSRESET\* drivers are located. Logic to interface an operator's panel and to detect power fail may also be placed on this circuit card.

FIGURE 5-5. Block Diagram of POWER MONITOR Module

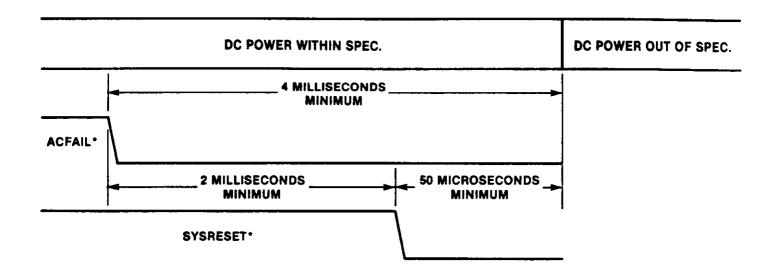

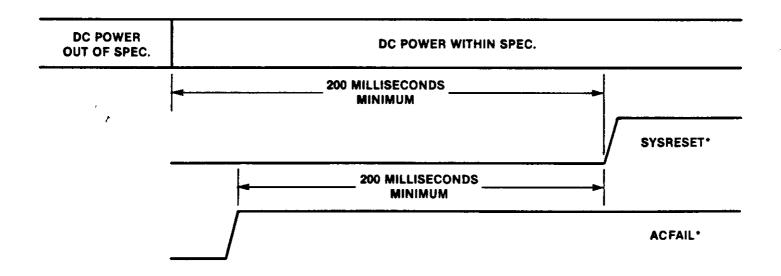

The ACFAIL\* and SYSRESET\* signals and the point at which the system DC voltages violate specification have certain timing constraints. These constraints are spelled out in Figures 5-6 and 5-7.

FIGURE 5-6. System Power Fail Timing

FIGURE 5-7. System Power Restart Timing

TABLE 7-1. Bus Voltage Specifications

| MAXIMUM<br>CURRENT DRAW<br>PER SLOT       | 8 amps       | e amps        | 3 amps        | 3 amps         | 3 amps       | 3 amps       |                                                                                 |                       |                                                                                                                                                                                                                |

|-------------------------------------------|--------------|---------------|---------------|----------------|--------------|--------------|---------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONNECTOR P2<br>PIN NUMBER                | 7 - 10       | 11 - 12       | 15 - 16       | ,              | 02 - 69      | 89 - 29      | 1-2, 3-4, 5-6,<br>97-98, 101-102                                                | 13 - 14               | wer will remain<br>resulting from                                                                                                                                                                              |

| CONNECTOR PI<br>PIN NUMBER                | 1,2,129-132  | 125 - 128     | 121 - 122     | 133 - 134      | ı            | 1            | 3,4,23-24,<br>27-28,31-32,<br>61-62,67-68,<br>71-72,119-120,<br>123-124,139-140 | •                     | The non-symetric variation spec is given to ensure that the DC power will remain within the ±5% tolerance required by most IC's despite any drops resulting from power distribution on individual VERSAboards. |

| RIPPLE & NOISE<br>BELOW 10 MHz<br>(PK-PK) | 50 mV        | 50 mV         | Уш 05         | 50 mV          | 25 mV        | 25 mV        | Ref.                                                                            | Ref.                  | ec is given to er<br>ired by most IC's<br>ual VERSAboards.                                                                                                                                                     |

| VARIATION<br>(see NOTE)                   | +5.08/-2.58  | +5.0%/-3.0%   | +3.0%/-5.0%   | +5.0%/-2.5%    | +5.0%/-3.0%  | +3.0%/-5.0%  | Ref.                                                                            | Ref.                  | The non-symetric variation spec is given to e<br>within the ±5% tolerance required by most IC°<br>power distribution on individual VERSAboards.                                                                |

| DESCRIPTION                               | +5 Vdc power | +12 Vdc power | -12 Vdc power | +5 Vdc standby | analog power | analog power | ground                                                                          | +15V ground<br>return |                                                                                                                                                                                                                |

| MNEMONIC                                  | +5V          | +12v          | -12v          | +5V STDBY      | +15V         | -15V         | Q.                                                                              | 15V GND               | NOTE:                                                                                                                                                                                                          |

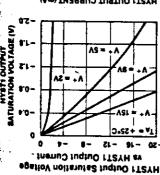

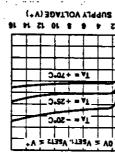

### 7.3 ELECTRICAL SIGNAL CHARACTERISTICS

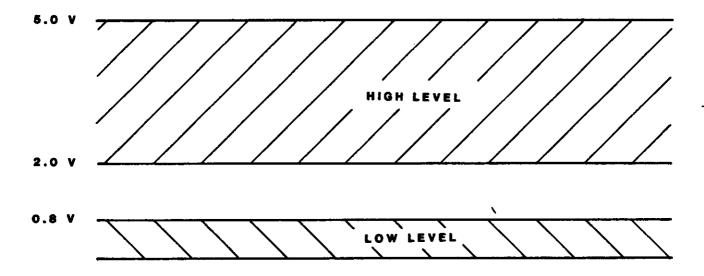

Other than power supply lines, all VERSAbus signals are limited to positive levels between 0 and 5.0 volts. As described in paragraph 1.4.1, the signal levels are:

a. 0.0 V  $\leq$  Low level  $\leq$  0.8 V b. 2.0 V  $\leq$  High level  $\leq$  5.0 V

Figure 7-1 gives a simple graphic representation of these levels.

FIGURE 7-1. VERSAbus Signal Levels

Depending on the function required, VERSAbus uses three-state, wired-OR, and totem pole drivers. The drivers are specified in paragraph 7.4, and the receivers are specified in paragraph 7.5. Appendix C lists signal lines by function, and gives their associated characteristics.

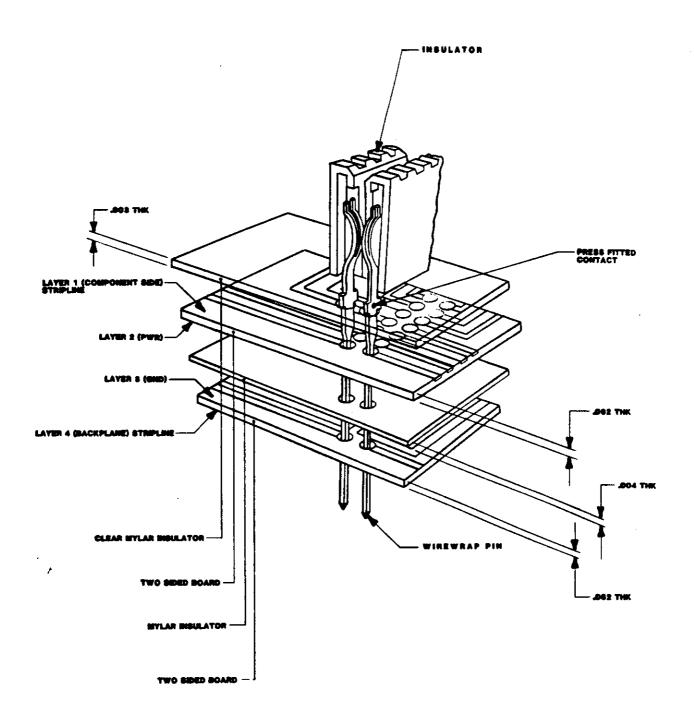

FIGURE 8-1. Typical Multilayer Backplane/PCB Construction Technique

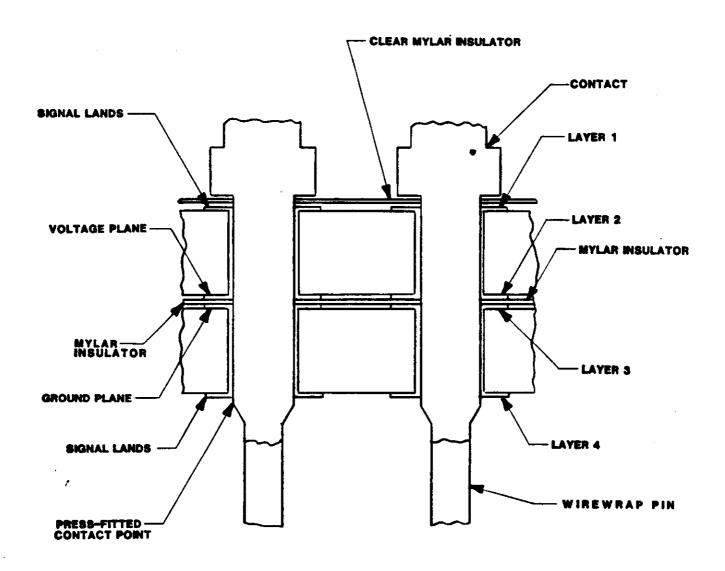

FIGURE 8-2. Typical Multilayer Backplane/PCB Cross-Sectional Area View

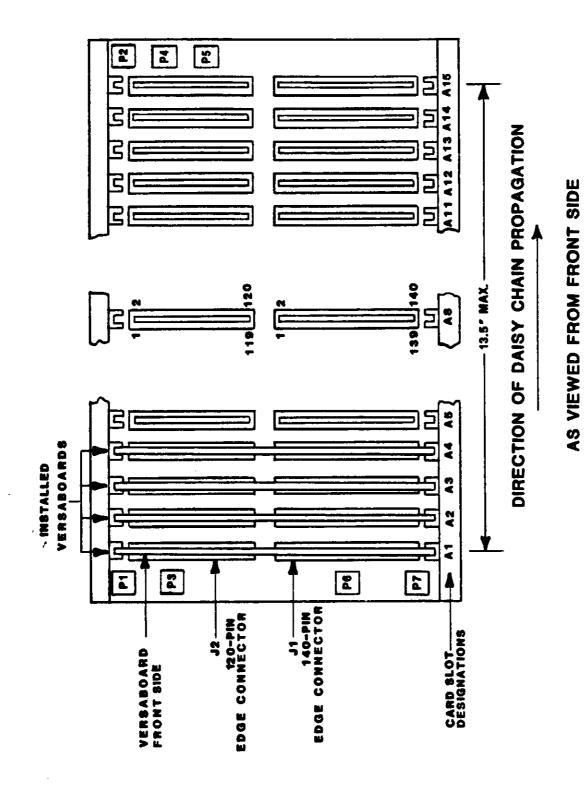

Backplane Reference Designations and Pin Numbering Standard FIGURE 8-3.

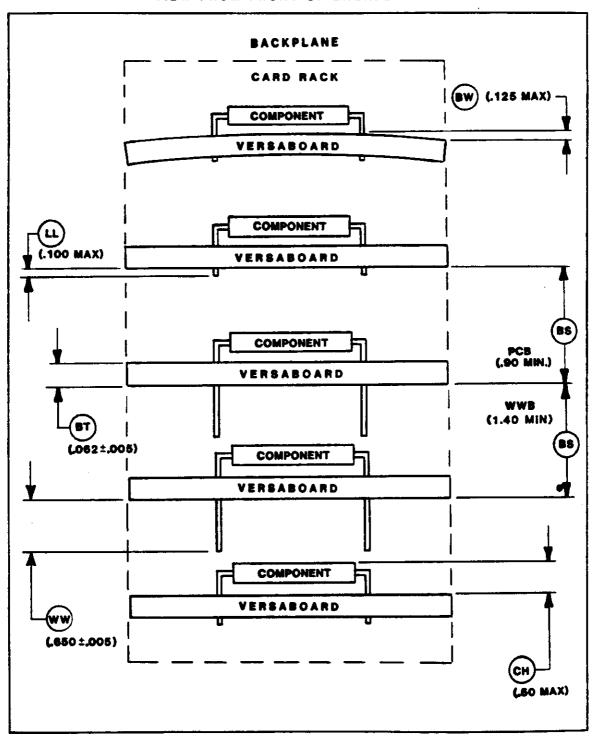

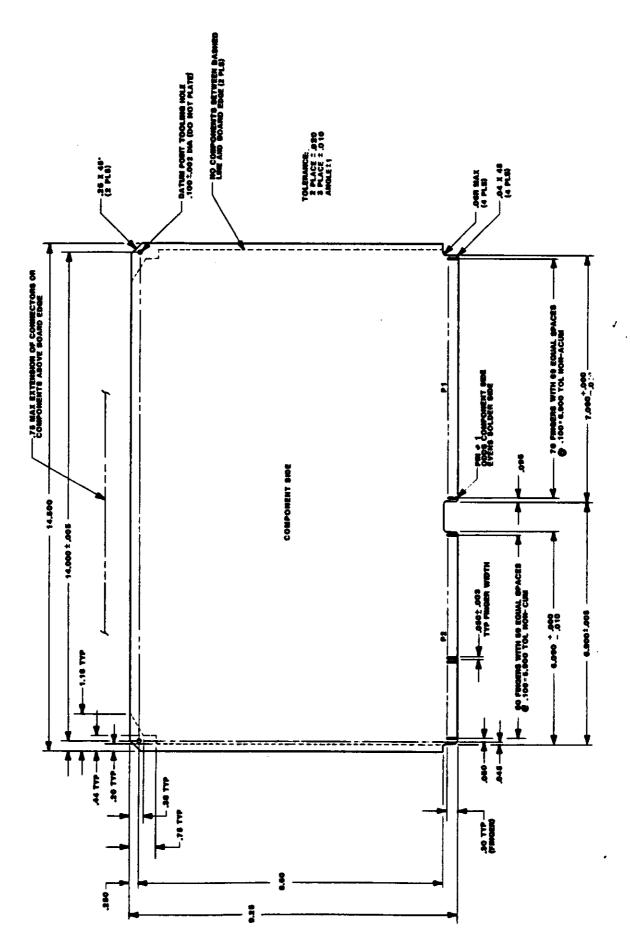

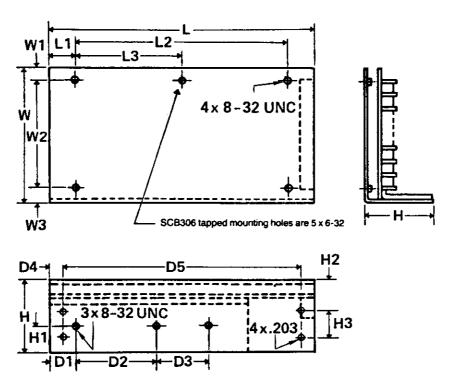

FIGURE 8-4. Backplane/VERSAboard Dimensional Requirements

#### CAUTION

THE ABOVE DIMENSIONS CAN VARY, DEPENDING ON MANUFACTURER.

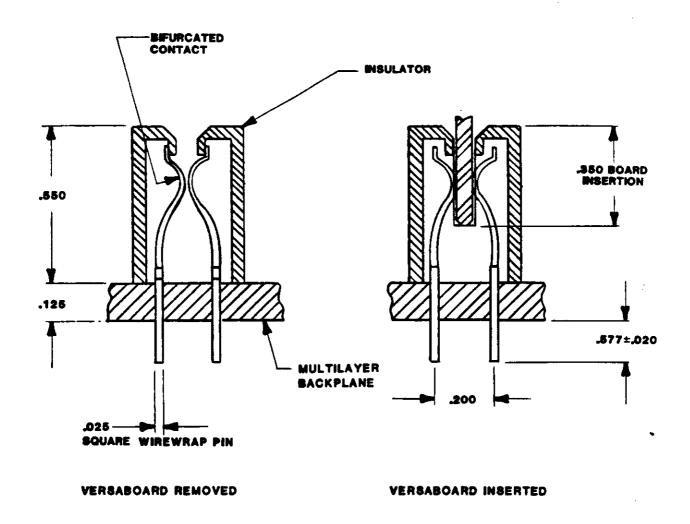

FIGURE 8-5. Typical Backplane Edge Connector

#### BACK SIDE OF BACKPLANE

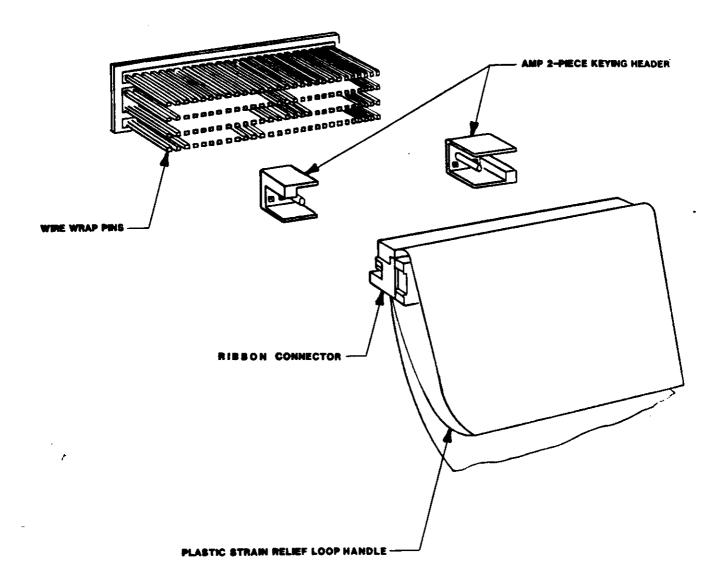

FIGURE 8-6. I/O Cable Connection

#### VIEW FROM FRONT SIDE OF VERSAboard

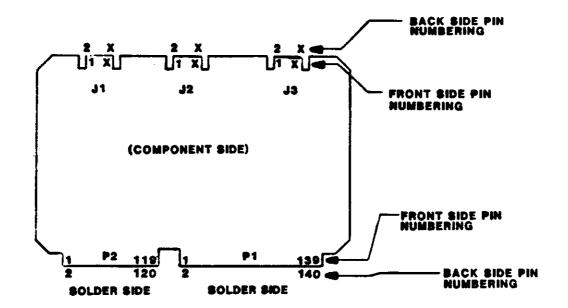

FIGURE 8-10. VERSAboard Reference Designations and Pin Numbering Standards

FIGURE 8-11. Standard Size PCB

#### APPENDIX A

#### GLOSSARY OF VERSABUS TERMS

- Axx\* the symbolic notation for a particular address line on the VERSAbus, where 'xx' may have the values 01 through 31. These lines are driven by the module currently designated as the VERSAbus MASTER to selectively address one and only one other module. The module is designated as the addressed SLAVE for the purpose of initiating a data transfer between two modules.

- the VERSAbus option which identifies a particular module as capable of driving or responding to only 23 address lines. (See the section on SUBSET compatibility for further information.)

- A32 the VERSAbus option which identifies a particular module as capable of driving or responding to all 31 address lines. (See the section on SUBSET compatibility for further information.)

- APARITYO\* the parity line associated with the signal lines AO1\* through A23\*, LWCRD\*, and AM0\* through AM7\*. This line represents the 'exclusive OR' of the 32 lines above. Therefore, the 'exclusive OR' of this line with all of those lines should always be zero. This condition is often referred to as even parity. If the MASTER currently in control of the VERSAbus and the SLAVE being addressed are both option AP (meaning: address parity), then the MASTER will generate this parity signal and the SLAVE will verify it. (See the section on SUBSET compatibility for further information on other combinations of MASTER and SLAVE options.)

- APARITY1\* the parity line associated with the signal lines A24\* through A31\*. This line represents the exclusive OR of these eight additional address lines used in extended addressing on the VERSAbus, Option A32. (See APARITY0\* for additional details and the section on SUBSET compatibility for information on combinations of MASTER and SLAVE options.)

- AP the option designated when a module will properly generate (if MASTER) or test (if SLAVE) address parity.

- APVAL\* a signal line driven low by AP MASTERS whenever they place an address on VERSAbus. This low level indicates to the addressed SLAVE that the APARITY lines are valid. If the SLAVE is option AP, it will verify this parity.

- ARBITER the term used to reference the logic circuitry connected to VERSAbus at slot 1 to perform the task defined as ARBITRATION.

(See ARBITRATION for additional definition. See the chapter on bus arbitration for detailed description.)

- ARBITRATION the task of assigning control of the data transfer bus on a priority basis to a requester. (For detailed material, see the chapter on bus arbitration.)

AS\*

- the address strobe line of the VERSAbus. When a MASTER has assumed control of the bus and has driven this line low, it is a signal to all SLAVES that the address bus is now valid and that a data transfer is initiated. The last act of a given MASTER in a data transfer cycle must be to release this line to the TRI-STATE condition, so that all units may know that this data transfer is over and that, if the 'bus busy' line is also released, the DTB is now available to be reassigned to the next MASTER. For detailed information on timing considerations, see the timing section of the Data Transfer Bus chapter.

BGxIN\*/BGxOUT\* - the symbolic notation used for a particular bus grant line on the VERSAbus, where 'x' may have the values 0 through 4. These lines are used to grant a particular level of data transfer bus access from the bus ARBITER, and represent a set of lines on the bus which are not bused, but daisy-chains. In particular, this nomenclature refers to the signal being forwarded to the next module in the chain. If this module does not use the particular level in question, the path from BGxIN\* to BGxOUT\* will probably be a jumper; but if this board uses the level, the signal will be passed through an AND gate, so that if the board receives the signal, and has a request pending, it may inhibit the signal from continuing down the bus and triggering activity on two MASTERS simultaneously. Not only does this methodology provide a means for having more MASTERS than levels of bus request, but it provides a secondary level of prioritization within a given level of bus request, which is physically determined by proximity to slot 1. (See also the chapter on bus arbitration.)

BRx\*

- the symbolic notation used for a particular bus request line on the VERSAbus, where 'x' may have the values 0 through 4. These lines are used to request control of data transfer bus access from the bus ARBITER.

Dxx\*

- the symbolic notation for a particular data line on the VERSAbus, where 'xx' may have the values 00 through 31. These lines are used by one module to selectively transfer data to one and only one other module.

DIB

- an acronym for DATA TRANSFER BUS. This is the particular subset of VERSAbus lines involved in a data transfer, consisting of the address lines, the address parity lines, the lines, the data parity lines, and the lines LWORD\*, WRITE\*, AS\*, DSO\*, DS1\*, DTACK\*, and BERR\*.

DPARITY0\*

- the parity line associated with the signal lines D00\* through D07\*. This line represents the 'exclusive OR' of those eight data lines. Therefore, the 'exclusive OR' of this line with all of those lines should always be zero. This condition is often referred to as even parity. If the module currently providing data to the VERSAbus is defined as having option DP, it will generate this signal. If the module currently receiving the data is defined as having option DP, it will verify this parity and flag errors. (See the section on SUBSET compatibility for further information on various combinations of options.)

- DPARITY1\* the parity line associated with the signal lines D08\* through D15\*. This line represents the 'exclusive OR' of eight of the data lines referenced by DS1\*. (See DPARITY0\* for more details.)

- DPARITY2\* the parity line associated with the signal lines D16\* through D23\*. This line represents the 'exclusive OR' of eight of the data lines used during longword transfers, and is only driven by modules having option D32. (See DPARITYO\* for more details on parity, and the section on SUBSET compatibility for further information on various combinations of options.)

- DPARITY3\* the parity line associated with the signal lines D24\* through D31\*. This line represents the 'exclusive CR' of eight of the data lines used during longword transfers, and can only exist on modules having option D32. (See DPARITY0\* for more details on parity, and the section on SUBSET compatibility for further information on various combinations of options.)

- DPVAL\* a signal line driven low by DP MASTERS and DP SLAVES whenever they place data on VERSAbus. This low level indicates to the MASTER/SLAVE receiving the data that the DPARITY lines are valid and may be used to verify data.

- DP the option designated when a module will generate data parity when presenting data, and test data parity when receiving data.

- LONGWORD a data transfer operation involving 32 bits of transferred data, which is invoked by a MASTER module driving the signal LWORD\* to the low state. Note that only modules classified as having option D32 can be expected to transfer long words. (See the section on SUBSET compatibility for further material.)

- LWORD\* the signal on the VERSAbus used to invoke 32-bit data transfers (See also LONGWORD.)

- MASTER a module capable of requesting control of the VERSAbus data transfer bus via its associated REQUESTER, and upon being signaled by its REQUESTER that the data transfer bus has been granted, is capable of addressing another module by driving the address lines and sending data to or receiving data from the module so addressed.

- NAP the option designated when a module will not generate (if MASTER) or test (if SLAVE) address parity.

- NDP the option designated when a module will not generate or test data parity.

- NPF the option designated for a VERSAbus ARBITER which does not have the additional logic on board to allow response to a system MASTER under emergency conditions such as power down. (See chapter on bus arbitration and definition of PF for further details.)

- the option designated for a VERSAbus ARBITER capable of responding to the BREL\* signal as an emergency bus request. (See chapter on bus arbitration for further details.)

READ

- a data transfer initiated by a MASTER, with the data flow from MASTER to SLAVE.

SLAVE

- a module capable of decoding the address lines of the VERSAbus, and properly responding to a MASTER by accepting or rejecting data transfers via the DTACK\* and BERR\* response lines when the address presented matches one recognized by this SLAVE as within its range.

System MASTER - a designation for that MASTER which has the responsibility for saving and restoring data at system power up, system power down, and other emergency handling. Through the use of a PF ARBITER, the system MASTER can gain quick control of the data transfer bus for emergency purposes.

WRITE

- a data transfer initiated by a MASTER, with the data flow from MASTER to SLAVE.

#### APPENDIX C

#### VERSAbus CONNECTOR/PIN DESCRIPTION

#### INTRODUCTION

This appendix describes the VERSAbus pin connections. The following table identifies the VERSAbus signals by signal mnemonic, connector and pin number, and signal characteristic. Unless otherwise specified, all signal lines are driven by the master.

#### VERSAbus Signal Identification

|                            | CONNECTOR                     |                                                                                                                                                                                                   |

|----------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIGNAL                     | AND                           | ,                                                                                                                                                                                                 |

| MNEMONIC                   | PIN NUMBER                    | SIGNAL NAME AND DESCRIPTION                                                                                                                                                                       |

| ACCLK                      | J1: 69                        | AC CLOCK - Open collector driven clock signal generated by the power monitor that indicates the power line frequency and zero voltage transition points.                                          |

| ACFAIL*                    | J1: 78                        | AC FAILURE - Open-collector driven signal which indicates that the AC input to the power supply is no longer being provided or that the required input voltage levels are not being met.          |

| ACKIN*                     | J1: 95                        | ACKNOWLEDGE IN - Totem-pole driven signal. ACKIN* and ACKOUT* signals form a daisy-chained acknowledge. The ACKIN* signal indicates to VERSAboard that an acknowledge cycle is in progress.       |

| ACKOUT*                    | Jl: 96                        | ACKNOWLEDGE OUT - Totem-pole driven signal. ACKIN* and ACKOUT* signals form a daisy-chained acknowledge. The ACKOUT* signal indicates to the next board that an acknowledge cycle is in progress. |

| <b>A</b> M0*- <b>A</b> M7* | J1: 59,60,<br>63,83-86,<br>94 | ADDRESS MODIFIER (bits 0-7) - Three-state driven lines that provide additional information about the address bus - such as size, cycle type, and/or DTB master identification.                    |

| APARITYO*                  | Jl: 33                        | ADDRESS PARITY 0 - Three-state driven signal which provides an even parity bit for address bits A01*-A23*, LWORD*, and AM0*-AM7*.                                                                 |

| APARITY1*                  | J2: 88                        | ADDRESS PARITY 1 - Three-state driven signal which provides an even parity bit for address bits A24*-A31* for use in 32-bit expansion.                                                            |

VERSAbus Signal Identification (cont'd)

| SIGNAL              | CONNECTOR<br>AND               |                                                                                                                                                                                                                                                                 |

|---------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MINEMONIC           | PIN NUMBER                     | SIGNAL NAME AND DESCRIPTION                                                                                                                                                                                                                                     |

| APVAL*              | J1: 117                        | ADDRESS PARITY VALID - Three-state driven signal that indicates that valid parity has been placed on the appropriate APARITY lines.                                                                                                                             |

| AS*                 | Jl: 30                         | ADDRESS STROBE - Three-state driven signal that indicates a valid address is on the address bus.                                                                                                                                                                |

| A01*-A23*           | J1: 36-58                      | ADDRESS bus (bits 1-23) - Three-state driven address lines that specify a memory address.                                                                                                                                                                       |

| A24*-A31*           | J2: 89-96                      | ADDRESS bus (bits 24-31) - Three-state driven optional address lines that specify an extended memory address.                                                                                                                                                   |

| BBSY*               | J1: 112                        | BUS BUSY - Open-collector driven signal generated<br>by the current DTB master to indicate that it is<br>using the bus.                                                                                                                                         |

| BCLR*               | J1: 113                        | BUS CLEAR - Totem-pole driven signal generated by<br>the bus arbitrator to request release by the<br>current DTB master in the event that a higher<br>level is requesting the bus.                                                                              |

| BERR*               | J1: 81                         | BUS ERROR - Open-collector driven signal generated<br>by a slave. This signal indicates that an<br>unrecoverable error has occurred and the bus cycle<br>must be aborted.                                                                                       |

| BG0IN*-<br>BG4IN*   | J1: 97,99,<br>101,103,<br>105  | BUS GRANT (0-4) IN - Totem-pole driven signals generated by the Arbiter or Requesters. Bus grant in and out signals form a daisy-chained bus grant. The bus grant signal indicates to this board that it may become the next bus master.                        |

| BG00UT*-<br>BG40UT* | J1: 98,100,<br>102,104,<br>106 | BUS GRANT (0-4) OUT - Totem-pole driven signals generated by Requesters. Bus grant in and out signals form a daisy-chained bus grant. The bus grant out signal indicates to the next board that it may become the next bus master.                              |

| BR0*-BR4*           | J1: 107-111                    | BUS REQUEST (0-4) - Open-collector driven signals generated by Requesters. These signals indicate that a DTB master in the daisy-chain requires access to the bus.                                                                                              |

| BREL*               | J1: 114                        | BUS RELEASE - Open-collector driven signal generated by an emergency requester to indicate to the current DTB master that the master must clear the bus within 16 data transfer cycles. It also informs the arbiter that a highest priority bus request exists. |

VERSAbus Signal Identification (cont'd)

| SIGNAL    | CONNECTOR<br>AND |                                                                                                                                                                                                                                                                       |

|-----------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC  | PIN NUMBER       | SIGNAL NAME AND DESCRIPTION                                                                                                                                                                                                                                           |

| DPARITYO* | J1: 21           | DATA PARITY 0 - Three-state driven bidirectional signal, generated by either the master or the slave, which provides an even parity bit for data bits D00*-D07*.                                                                                                      |

| DPARITY1* | J1: 22           | DATA PARITY 1 - Three-state driven bidirectional signal, generated by either the master or the slave, which provides an even parity bit for data bits D08*-D15*.                                                                                                      |

| DPARITY2* | J2: 103          | DATA PARITY 2 - Three-state driven bidirectional signal, generated by either the master or the slave, which provides an even parity bit for data bus D16*-D23*.                                                                                                       |

| DPARITY3* | J2: 104          | DATA PARITY 3 -Three-state driven bidirectional signal, generated by either the master or the slave, which which provides an even parity bit for data bits D24*-D31*.                                                                                                 |

| DPVAL*    | Jl: 118          | DATA PARITY VALID - Three-state driven bidirec-<br>tional signal that indicates during a data<br>transfer that valid parity has been placed on the<br>appropriate DPARITY lines.                                                                                      |

| DSO*      | Jl: 25           | DATA STROBE 0 - Three-state driven signal that indicates during byte and word transfers that a data transfer will occur on data bus lines (D00*-D07*).                                                                                                                |

| DS1*      | J1: 26           | DATA STROBE 1 - Three-state driven signal that indicates during byte and word transfers that a data transfer will occur on data bus lines (D08*-D15*).                                                                                                                |

| DTACK*    | J1: 29           | DATA TRANSFER ACKNOWLEDGE - Open-collector driven signal generated by a DTB slave. The falling edge of this signal indicates that valid data is available on the data bus during a read cycle, or that data has been accepted from the data bus during a write cycle. |

| D00*-D15* | J1: 5-20         | DATA BUS (bits 0-15) - Three-state driven bidirectional data lines that provide a data path between the DTB master and slave.                                                                                                                                         |

| D16*-D31* | J2: 105-120      | DATA BUS (bits 16-31) - Three-state driven bidirectional data lines that provide an expanded data path between the DTB master and slave for the optional expanded data bus configuration (option EADB).                                                               |

VERSAbus Signal Identification (cont'd)

| Γ           |                                                    |                                                                                                                                                                                                                                                              |

|-------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIGNAL      | CONNECTOR<br>AND                                   |                                                                                                                                                                                                                                                              |

| MNEMONIC    | PIN NUMBER                                         | SIGNAL NAME AND DESCRIPTION                                                                                                                                                                                                                                  |

| <b>G</b> ND | J1: 3,4,23,<br>24,27,28,<br>31,32,61,<br>62,67,68, | GROUND                                                                                                                                                                                                                                                       |

|             | 71,72,<br>119,120,<br>123,124,<br>135-140          |                                                                                                                                                                                                                                                              |

| GND         | J2: 1-6                                            | GROUND                                                                                                                                                                                                                                                       |

| GND         | J2: 97,98,<br>101,102                              | GROUND (EXPANDED BUS OPTION ONLY)                                                                                                                                                                                                                            |

| QND (+15V)  | J2: 13,14                                          | ANALOG GROUND                                                                                                                                                                                                                                                |

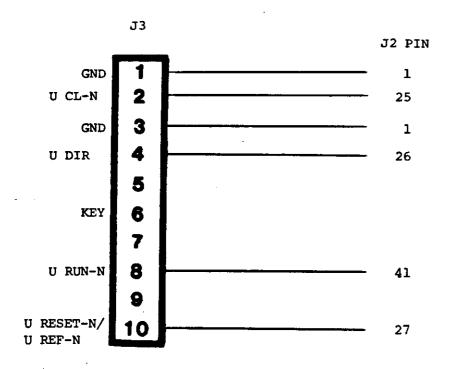

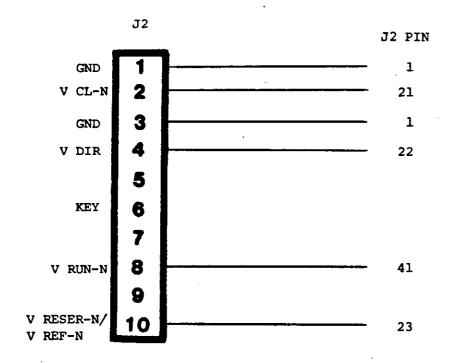

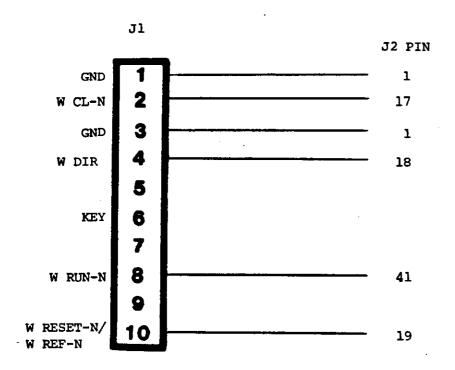

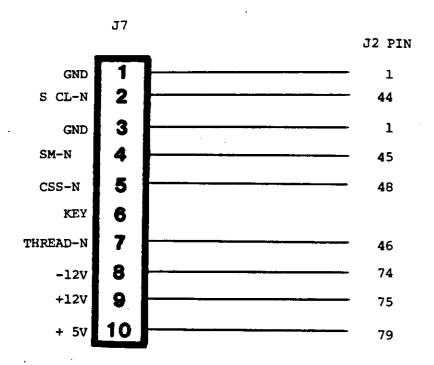

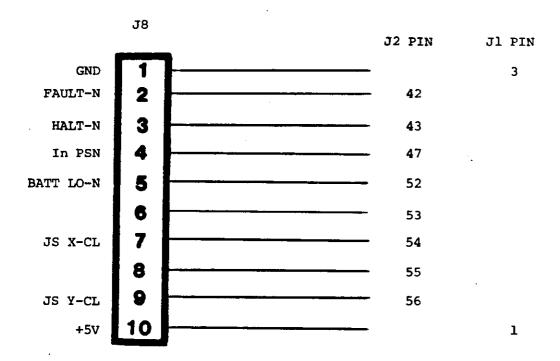

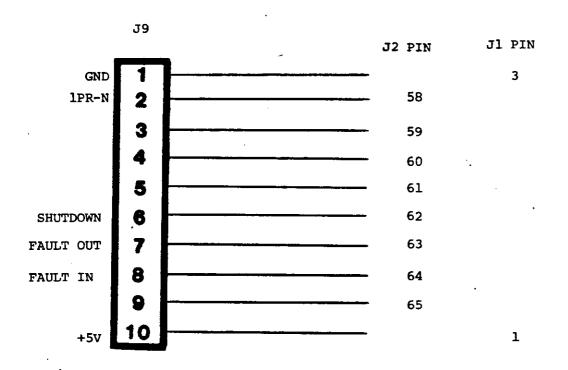

| [1/O PIN]   | J2: 17-66                                          | <pre>INPUT/OUTPUT PIN - I/O signal lines set aside for<br/>user peripheral interfacing applications on<br/>expanded bus backplanes.</pre>                                                                                                                    |

|             | J2: 17-66,<br>71-120                               | INPUT/OUTPUT PIN - I/O signal lines set aside for user peripheral interfacing applications on non-expanded bus backplanes.                                                                                                                                   |

| IRQ1*~IRQ7* | J1: 87-93                                          | INTERRUPT REQUEST (1-7) - Open-collector driven signals, generated by an interrupter, which carry prioritized interrupt requests. Level seven is the highest priority.                                                                                       |

| LWORD*      | J1: 35                                             | LONGWORD - Three-state driven signal specifying that the cycle is a byte/word transfer (when high) or a longword transfer (when low). LONGWORD transfers are only possible between an option D32 MASTER and an option D32 SLAVE using an expanded backplane. |

| [RESERVED]  | J1: 64,66,<br>73,75,76,<br>77,82,<br>115-116       | RESERVED - Signal lines reserved for future VERSAbus enhancements These lines must not be used by users.                                                                                                                                                     |

|             | J2: 71-87,<br>99,100                               | RESERVED - (EXPANDED BUS backplanes ONLY.)                                                                                                                                                                                                                   |

| SYSCLK      | J1: 70                                             | SYSTEM CLOCK - A constant 16 MHz clock signal that is independent of processor speed or timing. This signal is used for general system timing use.                                                                                                           |

| ,           |                                                    |                                                                                                                                                                                                                                                              |

VERSAbus Signal Identification (cont'd)

| SIGNAL<br>MNEMONIC | CONNECTOR AND PIN NUMBER        | SIGNAL NAME AND DESCRIPTION                                                                                                                                                                        |

|--------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSFAIL*           | J1: 80                          | SYSTEM FAIL - Open-collector driven signal that indicates that a failure has occurred in the system. This signal may be generated by any module on the VERSAbus.                                   |

| SYSRESET*          | J1: 74                          | SYSTEM RESET - Open-collector driven signal which, when low, will cause the system to be reset.                                                                                                    |

| TESTO*-<br>TEST1*  | J1: 65<br>79                    | SYSTEM TEST - Open collector driven signals that specify the mode to be entered when the SYSRESET* line is released.                                                                               |

| Write*             | J1: 34                          | WRITE - Three-state driven signal that specifies the data transfer cycle in progress to be either read or write. A high level indicates a read operation; a low level indicates a write operation. |

| +5V STDBY          | J1: 133-134                     | +5 Vdc STANDBY - This line supplies +5 Vdc to devices requiring battery backup.                                                                                                                    |

| +5v                | J1: 1,2,<br>129-132<br>J2: 7-10 | +5 Vdc Power - Used by system logic circuits.                                                                                                                                                      |

| +12V               | J1: 125-128<br>J2: 11,12        | +12 Vdc Power - Used by system logic circuits.                                                                                                                                                     |

| ,+15V              | J2: 69,70                       | +15 Vdc Power - Used by system analog circuits.                                                                                                                                                    |

| -12V               | J1: 121,122<br>J2: 15,16        | -12 Vdc Power - Used by system logic circuits.                                                                                                                                                     |

| -15V               | J2: 67,68                       | -15 Vdc Power - Used by system analog circuits.                                                                                                                                                    |

#### APPENDIX D

# VERSABUS BACKPLANE EDGE CONNECTOR J1 AND

#### VERSAboard EDGE CONNECTOR Pl

#### IDENTIFICATION

#### INTRODUCTION

This appendix identifies the VERSAbus backplane edge connector  ${\tt Jl/Pl}$  pin assignments. The following table lists the pin assignments by pin number order.

Jl/Pl Pin Assignments

| ODD PIN<br>NUMBER<br>(P1 COMPONENT SIDE) | SIGNAL<br>MNEMONIC | EVEN PIN<br>NUMBER<br>(P1 SOLDER SIDE) | SIGNAL<br>MNEMONIC |

|------------------------------------------|--------------------|----------------------------------------|--------------------|

| _                                        |                    |                                        |                    |

| 1                                        | +5V                | 2                                      | +5V                |

| 3                                        | GND                | 4                                      | GND                |

| 5<br>7                                   | D00*               | 6                                      | D01*               |

|                                          | D02*               | 8                                      | D03*               |

| 9                                        | D04*               | 10                                     | D05*               |

| , <b>11</b>                              | D06*               | 12                                     | D07*               |

| 13                                       | D08*               | 14                                     | D09*               |

| 15                                       | D10*               | 16                                     | D11*               |

| 17                                       | D12*               | 18                                     | D13*               |

| 19                                       | D14*               | 20                                     | D15*               |

| 21                                       | DPARITY0*          | 22                                     | DPARITY1*          |

| 23                                       | GND                | 24                                     | GND                |

| 25                                       | DS0*               | 26                                     | DS1*               |

| 27                                       | GND                | <b>2</b> 8                             | <b>GN</b> D        |

| 29                                       | DTACK*             | 30                                     | AS*                |

| 31                                       | GND                | 32                                     | GND                |

| 33                                       | APARITY0*          | 34                                     | WRITE*             |

| 35                                       | LWORD*             | 36                                     | A01*               |

| 37                                       | A02*               | <b>3</b> 8                             | A03*               |

| <b>3</b> 9                               | A04*               | 40                                     | A05*               |

| 41                                       | A06*               | 42                                     | A07*               |

| 43                                       | A08*               | 44                                     | A09*               |

| 45                                       | A10*               | 46                                     | A11*               |

| 47                                       | A12*               | 48                                     | A13*               |

| 49                                       | A14*               | 50                                     | A15*               |

| 51                                       | A16*               | 52                                     | A17*               |

| 53                                       | A18*               | 54                                     | A19*               |

| 55                                       | A20*               | 56                                     | A21*               |

| 57                                       | A22*               | 58                                     | A23*               |

| 59                                       | AM4*               | 60                                     | AM7*               |

| 61                                       | GND                | 62                                     | GND                |

| 63                                       | AM3*               | 64                                     | [RESERVED]         |

| 65                                       | TESTO*             | 66                                     | [RESERVED]         |

J1/P1 Pin Assignments (cont'd)

| ODD PIN<br>NUMBER<br>(Pl COMPONENT SIDE) | SIGNAL<br>MNEMONIC | EVEN PIN<br>NUMBER<br>(P1 SOLDER SIDE) | SIGNAL<br>MNEMONIC |

|------------------------------------------|--------------------|----------------------------------------|--------------------|

| 67                                       |                    |                                        | 45                 |

| 67                                       | GND                | 68<br>70                               | GND                |

| 69<br>71                                 | ACCLK<br>GND       | 70<br>72                               | SYSCLK<br>GND      |

| 73                                       | [RESERVED]         | 72<br>74                               | SYSRESET*          |

| 75                                       | [RESERVED]         | 74<br>76                               | [RESERVED]         |

| 77                                       | [RESERVED]         | 76<br>78                               | ACFAIL*            |

| 79                                       | TEST1*             | 80                                     | SYSFAIL*           |

| 81                                       | BERR*              | 82                                     | [RESERVED]         |

| 83                                       | AMO*               | 84                                     | AM1*               |

| 85                                       | AM2*               | 86                                     | AM6*               |

| 87                                       | IRO1*              | · <b>88</b>                            | IRO2*              |

| 89                                       | IRQ3*              | 90                                     | IRQ4*              |

| 91                                       | IRQ5*              | 92                                     | IRQ6*              |

| 93                                       | IRO7*              | 94                                     | AM5*               |

| 95                                       | ACKIN*             | 96                                     | ACKOUT*            |

| 97                                       | BGOIN*             | 98                                     | BGOOUT*            |

| 99                                       | BG1IN*             | 100                                    | BG10UT*            |

| 101                                      | BG2IN*             | 102                                    | BG20UT*            |

| 103                                      | BG3IN*             | 104                                    | BG3OUT*            |

| 105                                      | BG4IN*             | 106                                    | BG40UT*            |

| 107                                      | BRO*               | 108                                    | BR1*               |

| 109                                      | BR2*               | 110                                    | BR3*               |

| 111                                      | BR4*               | 112                                    | BBSY*              |

| 113                                      | BCLR*              | 114                                    | BREL*              |

| 115                                      | [RESERVED]         | 116                                    | [RESERVED]         |

| 117                                      | APVAL*             | 118                                    | DPVAL*             |

| 119                                      | <b>G</b> ND        | 120                                    | <b>GND</b>         |

| 121                                      | -12V               | 122                                    | -12V               |

| 123                                      | <b>G</b> ND        | 124                                    | <b>G</b> ND        |

| 125                                      | +1 <i>2</i> V      | 126                                    | +12V               |

| 127                                      | +12V               | 128                                    | +12V               |

| 129                                      | +5V                | 130                                    | +5V                |

| 131                                      | +5V                | 132                                    | +5V                |

| 133                                      | +5V STDBY          | 134                                    | +5V STOBY          |

| 135                                      | <b>G</b> ND        | 136                                    | <b>G</b> ND        |

| 137                                      | GND                | 138                                    | <b>GN</b> D        |

| 139                                      | GND                | 140                                    | GND                |

#### APPENDIX E

### VERSAbus BACKPLANE EDGE CONNECTOR J2

#### AND

### VERSAboard EDGE CONNECTOR P2

#### **IDENTIFICATION**

#### INTRODUCTION

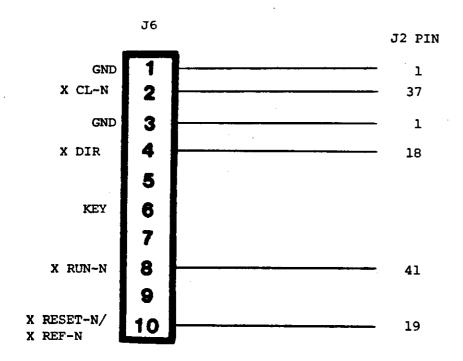

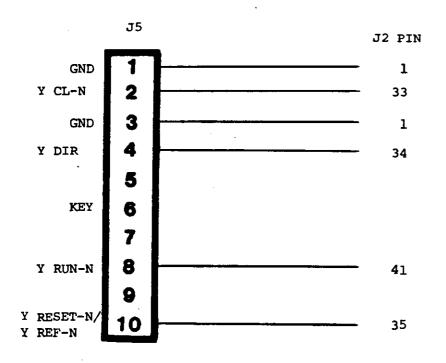

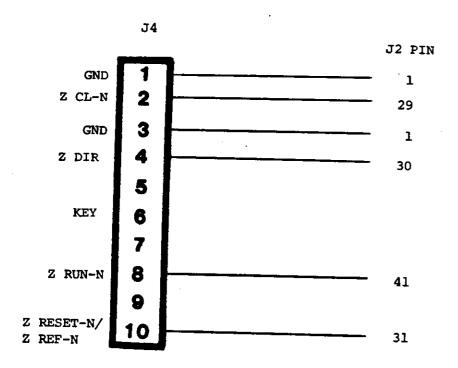

This appendix identifies the VERSAbus backplane edge connector J2 pin assignments. Table 1 lists the J2/P2 pin assignments by pin number order for the expanded bus option. Table 2 lists the J2/P2 pin assignments for the non-expanded bus option.

TABLE 1. J2/P2 Pin Assignments for the Expanded Bus Option

|                     | 1                   |                  | r           |

|---------------------|---------------------|------------------|-------------|

| ODD PIN             | }                   | EVEN PIN         |             |

| NUMBER              | SIGNAL              | NUMBER           | SIGNAL      |

| (P2 COMPONENT SIDE) | MINEMONIC           | (P2 SOLDER SIDE) | MNEMONIC    |

|                     |                     | _                |             |

| 1                   | <b>GN</b> D         | 2                | GND         |

| 3                   | GND                 | 4                | <b>GND</b>  |

| 5<br>7              | <b>GN</b> D         | 6                | <b>GND</b>  |

|                     | +5V                 | 8                | +5V         |

| 9                   | +5V                 | 10               | +5V         |

| 11                  | +12V                | 12               | +12V        |

| 13                  | GND ( <u>†</u> 15V) | 14               | GND (± 15V) |

| 15                  | -12V                | 16               | -12V        |

| 17                  | [I/O PIN]           | 18               | [I/O PIN]   |

| 19                  | [I/O PIN]           | 20               | [I/O PIN]   |

| 21                  | [I/O PIN]           | <b>2</b> 2       | [I/O PIN]   |

| 23                  | [I/O PIN]           | 24               | [I/O PIN]   |

| 25                  | [I/O PIN]           | 26               | [I/O PIN]   |

| 27                  | [I/O PIN]           | <b>2</b> 8       | [I/O PIN]   |

| ′ 29                | [I/O PIN]           | 30               | [I/O PIN]   |

| 31                  | [I/O PIN]           | 32               | [I/O PIN]   |

| 33                  | [I/O PIN]           | 34               | [I/O PIN]   |

| 35                  | [I/O PIN]           | <b>3</b> 6       | [I/O PIN]   |

| 37                  | [I/O PIN]           | 38               | [I/O PIN]   |

| 39                  | [I/O PIN]           | <b>4</b> 0       | [I/O PIN]   |

| <b>4</b> 1          | [I/O PIN]           | 42               | [I/O PIN]   |

| 43                  | [I/O PIN]           | 44               | [I/O PIN]   |

| 45                  | [I/O PIN]           | 46               | [I/O PIN]   |

| 47                  | [I/O PIN]           | 48               | [I/O PIN]   |

| 49                  | [I/O PIN]           | 50               | [I/O PIN]   |

| 51                  | [I/O PIN]           | 52               | [I/O PIN]   |

| 53                  | [I/O PIN]           | 54               | [I/O PIN]   |

| 55                  | [I/O PIN]           | 56               | [I/O PIN]   |

| 57                  | [I/O PIN]           | 58               | [I/O PIN] ' |

| 59                  | [I/O PIN]           | <b>6</b> 0       | [I/O PIN]   |

|                     | 1                   |                  |             |

| l .                 | Į į                 |                  | t           |

TABLE 1. J2/P2 Pin Assignments for the Expanded Bus Option (cont'd)

| ODD PIN<br>NUMBER<br>(P2 COMPONENT SIDE) | SIGNAL<br>MNEMONIC | EVEN PIN<br>NUMBER<br>(P2 SOLDER SIDE) | SIGNAL<br>MINEMONIC |

|------------------------------------------|--------------------|----------------------------------------|---------------------|

| 61                                       | [I/O PIN]          | 62                                     | [I/O PIN]           |

| 63                                       | [I/O PIN]          | 64                                     | [I/O PIN]           |

| 65                                       | [I/O PIN]          | <b>6</b> 6                             | [I/O PIN]           |

| 67                                       | -15V               | 68                                     | -15V                |

| 69                                       | +15V               | <b>7</b> 0 ′                           | +15V                |

| <b>7</b> 1                               | [RESERVED]         | <b>7</b> 2                             | [RESERVED]          |

| 73                                       | [RESERVED]         | 74                                     | [RESERVED]          |

| 75                                       | [RESERVED]         | 76                                     | [RESERVED]          |

| <b>7</b> 7                               | [RESERVED]         | <b>7</b> 8                             | [RESERVED]          |

| 79                                       | [RESERVED]         | <b>8</b> 0                             | [RESERVED]          |

| 81                                       | [RESERVED]         | 82                                     | [RESERVED]          |

| 83                                       | [RESERVED]         | 84                                     | [RESERVED]          |

| 85                                       | [RESERVED]         | <b>8</b> 6                             | [RESERVED]          |

| 87                                       | [RESERVED]         | 88                                     | APARITY1*           |

| 89                                       | A24*               | 90                                     | A25*                |

| 91                                       | A26*               | 92                                     | A27*                |

| 93                                       | A28*               | 94                                     | A29*                |

| 95                                       | A30*               | 96                                     | A31*                |

| 97                                       | GND                | 98                                     | GND                 |

| 99                                       | [RESERVED]         | 100                                    | [RESERVED]          |

| 101                                      | GND                | 102                                    | GND                 |

| 103                                      | DPARITY2*          | 104                                    | DPARITY3*           |

| 105                                      | D16*               | 106                                    | D17*                |

| 107                                      | D18*               | 108                                    | D19*                |

| 109                                      | D20*               | 110                                    | D21*                |

| 111                                      | D22*               | 112                                    | D23*                |

| 113                                      | D24*               | 114                                    | D25*                |

| 115                                      | D26*               | 116                                    | D27*                |

| 117                                      | D28*               | 118                                    | D29*                |

| 119                                      | D30*               | 120                                    | D31*                |

|                                          | <u> </u>           | <u> </u>                               | 1                   |

NOTE: Pins 17 through 66 are not bussed together by the backplane.

TABLE 2. J2/P2 Pin Assignments for the Non-Expanded Bus Option

| ODD PIN<br>NUMBER   | SIGNAL      | EVEN PIN NUMBER  | SIGNAL        |

|---------------------|-------------|------------------|---------------|

| (P2 COMPONENT SIDE) | MINEMONIC   | (P2 SOLDER SIDE) | MINEMONIC     |

| _                   |             | _                |               |

| 1                   | GND         | 2                | GND           |

| 3                   | <b>GN</b> D | 4                | GND           |

| 3<br>5<br>7         | GND         | 6                | GND           |

|                     | +5V         | 8                | +5V           |

| 9                   | +5V         | 10               | +5V           |

| 11                  | +12V        | 12               | +1 <i>2</i> V |

| 13                  | GND (± 15V) | 14               | GND (± 15V)   |

| 15                  | -12v        | 16               | -12V          |

| 17                  | [I/O PIN]   | 18               | [I/O PIN]     |

| 19                  | [I/O PIN]   | 20               | [1/O PIN]     |

| 21                  | [I/O PIN]   | 22               | [I/O PIN]     |

| 23                  | [I/O PIN]   | 24               | [I/O PIN]     |

|                     |             | 26               | [I/O PIN]     |

| 25<br>27            | [I/O PIN]   | 28               |               |

| 27                  | [I/O PIN]   |                  | [I/O PIN]     |

| 29                  | [I/O PIN]   | 30               | [I/O PIN]     |

| 31                  | [I/O PIN]   | 32               | [I/O PIN]     |

| 33                  | [I/O PIN]   | 34               | [I/O PIN]     |

| <b>3</b> 5          | [I/O PIN]   | 36               | [I/O PIN]     |

| 37                  | [I/O PIN]   | <b>3</b> 8       | [I/O PIN]     |

| 39                  | [I/O PIN]   | 40               | [1/O PIN]     |

| 41                  | [1/O PIN]   | 42               | [I/O PIN]     |

| 43                  | [I/O PIN]   | 44               | [I/O PIN]     |

| 45                  | [I/O PIN]   | 46               | [I/O PIN]     |

| 47                  | [I/O PIN]   | 48               | [I/O PIN]     |

| <b>4</b> 9          | [I/O PIN]   | 50               | [I/O PIN]     |

|                     |             | 52               | [I/O PIN]     |

| 51<br>53            | [I/O PIN]   | 52<br>54         | [I/O PIN]     |

| 53<br>55            | [I/O PIN]   |                  |               |

| 55                  | [I/O PIN]   | 56<br>50         | [I/O PIN]     |

| 57                  | [I/O PIN]   | 58               | [I/O PIN]     |

| 59                  | [I/O PIN]   | 60               | [I/O PIN]     |

| 61                  | [I/O PIN]   | 62               | [I/O PIN]     |

| <sup>7</sup> 63     | [I/O PIN]   | 64               | [I/O PIN]     |

| <b>65</b>           | [I/O PIN]   | <b>6</b> 6       | [I/O PIN]     |

| 67                  | -15V        | 68               | -15V          |

| 69                  | +15V        | 70               | +15V          |

| 71                  | [I/O PIN]   | 72               | [I/O PIN]     |

| 73                  | [I/O PIN]   | 74               | [I/O PIN]     |

| <b>7</b> 5          | [I/O PIN]   | 76               | [I/O PIN]     |

| 77                  | [I/O PIN]   | 78               | [I/O PIN]     |

| 79                  | [I/O PIN]   | 80               | [I/O PIN]     |

| 81                  | [I/O PIN]   | 82               | [I/O PIN]     |

|                     |             | 84               | [I/O PIN]     |

| 83                  | [I/O PIN]   |                  |               |

| <b>8</b> 5          | [I/O PIN]   | 86               | [I/O PIN]     |

| 87                  | [I/O PIN]   | 88               | [I/O PIN]     |

| <sub>.</sub> 89     | [I/O PIN]   | 90               | [I/O PIN]     |

| 91                  | [I/O PIN]   | 92               | [I/O PIN] ,   |

| 93                  | [I/O PIN]   | 94               | [I/O PIN]     |

| <b>9</b> 5          | [I/O PIN]   | 96               | [I/O PIN]     |

|                     |             | ł                |               |

|                     |             |                  | ļ             |

|                     | •           | •                | -             |

TABLE 2. J2/P2 Pin Assignments for the Non-Expanded Bus Option (cont'd)

| ODD PIN<br>NUMBER<br>(P2 COMPONENT SIDE) | SIGNAL<br>MNEMONIC | EVEN PIN NUMBER (P2 SOLDER SIDE) | SIGNAL<br>MNEMONIC |

|------------------------------------------|--------------------|----------------------------------|--------------------|

| 97                                       | [I/O PIN]          | 98                               | [I/O PIN]          |

| 99                                       | [I/O PIN]          | 100                              | [I/O PIN]          |

| 101                                      | [I/O PIN]          | 102                              | [I/O PIN]          |

| 103                                      | [I/O PIN]          | 104                              | [I/O PIN]          |

| 105                                      | [I/O PIN]          | 106                              | [I/O PIN]          |

| 107                                      | [I/O PIN]          | 108                              | [I/O PIN]          |

| 109                                      | [I/O PIN]          | 110                              | [I/O PIN]          |

| 111                                      | [I/O PIN]          | 112                              | [I/O PIN]          |

| 113                                      | [I/O PIN]          | 114                              | [I/O PIN]          |

| 115                                      | [I/O PIN]          | 116                              | [I/O PIN]          |

| 117                                      | [I/O PIN]          | 118                              | [I/O PIN]          |

| 119                                      | [I/O PIN]          | 120                              | [I/O PIN]          |

NOTE: Pins 17 through 66 and pins 71 through 120 are not bussed together by the backplane.

BUS DRIVER AND RECEIVER SUMMARY

| SIGNAL                        | SIGNAL                   | DRIVER        | ER                                  | RECEIVER                                  | TERMINATION |

|-------------------------------|--------------------------|---------------|-------------------------------------|-------------------------------------------|-------------|

| MNEMONIC                      | NAME                     | TYPE          | MODULE                              | MODULE                                    | NETWORK     |

| A01*-A31*<br>(31 lines)       | ADDRESS BUS              |               |                                     |                                           |             |

| AMO*-AM7*<br>(8 lines)        | ADDRESS MODIFIER         | o contraction | SCHOOL STATE                        | C. AVIDC                                  | VPC         |

| AS*                           | ADDRESS STROBE           | IPREE         | INTERRUPT HANDLERS                  | INTERRUPTERS                              | S31         |

| LWORD*                        | LONGMORD                 |               |                                     |                                           |             |

| WRITE*                        | WRITE                    |               |                                     |                                           |             |

| DSO*-DS1*<br>(2 lines)        | DATA STROBES             |               |                                     |                                           |             |

| D00*-D31*<br>(32 lines)       | DATA BUS                 | THREE         | MASTERS,<br>SLAVES,<br>INTERRUPTERS | SLAVES,<br>MASTERS,<br>INTERRUPT HANDLERS | YES         |

| DTACK*                        | DATA TRANSFER ACKNOWEDGE | 8             | SLAVES,<br>INTERRUPTERS             | MASTERS,<br>INTERRUPT HANDLERS            | YES         |

| BERR*                         | BUS ERROR                | 8             | SLAVES                              | MASTERS                                   | YES         |

| DPARITYO*-DPARITY3* (4 lines) | DATA PARITY              | THREE         | DP MASTERS<br>DP SLAVES             | DP SLAVES<br>DP MASTERS                   | YES         |

| DPVAL*                        | DATA PARITY VALID        | THREE         | DP MASTERS<br>DP SLAVES             | DP MASTERS<br>DP SLAVES                   | YES         |

| APARITYO*-APARITY1* (2 lines) | ADDRESS PARITY           | THREE         | AP MASTERS                          | AP SLAVES                                 | YES         |

| APVAL*                        | ADDRESS PARITY VALID     | THREE         | AP MASTERS                          | AP SLAVES                                 | YES         |

#### APPENDIX F

#### DC SIGNAL SPECIFICATION

This appendix provides a summary showing which signal lines on VERSAbus are driven/received by each functional module, and the type of driver each uses.

In order to simplify the table, an abbreviated notation is used to describe the various types of drivers. The notations used are shown below:

Totem pole (high current) - TP HC

Totem pole (low current) - TP LC

Three-state - THREE

Open collector - OC

For the driver specifications, see Table 7-2 in Chapter 7.

All functional modules use the same type of receiver. (For the receiver specifications, see Table 7-3 in Chapter 7.)

BUS DRIVER AND RECEIVER SUMMARY (cont'd)

| SIGNAL                       | SIGNAL                     | DRIV    | ER                                  | RECEIVER                     | TERMINATION |

|------------------------------|----------------------------|---------|-------------------------------------|------------------------------|-------------|

| MNEMONIC                     | NAME                       | TYPE MO | MODULE                              | MODULE                       | NETWORK     |

| BRO*-BR4*<br>(5 lines)       | BUS REQUEST                | 8       | REQUESTERS                          | ARBITER                      | Säx         |

| BG01N*-BG41N*<br>(5 lines)   | BUS GRANT                  | 71 ALC  | ARBITER                             | REQUESTERS                   | Q.          |

| BGOOUT*-BG4OUT*<br>(5 lines) |                            |         | REQUESTERS                          | (NOT APPLICABLE)             | ON          |

| BBSY*                        | BUS BUSY                   | 8       | EMERGENCY REQUESTER                 | ARBITER                      | YES         |

| BCLR*                        | BUS CLEAR                  | TP HC   | ARBITER                             | MASTERS                      | YES         |

| BREL*                        | BUS RELEASE                | TP HC   | EMERGENCY REQUESTER                 | MASTERS                      | YES         |

| IRQ1*-IRQ7*<br>(7 lines)     | INTERRUPT REQUEST          | ည       | INTERRUPTERS                        | INTERRUPT HANDLERS           | YES         |